# Testing and Validation of Phasor Measurement Based Devices and Algorithms

Final Project Report

Empowering Minds to Engineer the Future Electric Energy System

# Testing and Validation of Phasor Measurement Based Devices and Algorithms

# **Final Project Report**

# **Project Team**

Anurag K Srivastava, Project Leader Saugata S Biswas, Graduate Student Washington State University

A. P. Sakis Meliopoulos Evangelos Polymeneas, Graduate Student Yonghee Lee, Graduate Student Georgia Institute of Technology

**PSERC Publication 13-44**

September 2013

# For information about this project, contact

Anurag K Srivastava, Project Leader

Assistant Professor, The School of Electrical Engineering and Computer Science

Director, Smart Grid Demonstration and Research Investigation Lab (SGDRIL)

Energy Systems Innovation Center (ESIC)

Washington State University

355 Spokane St, Pullman, Washington 99164-2752

Phone: 509-335-2348 Fax: 509-335-3818

Email: asrivast@eecs.wsu.edu

# **Power Systems Engineering Research Center**

The Power Systems Engineering Research Center (PSERC) is a multi-university Center conducting research on challenges facing the electric power industry and educating the next generation of power engineers. More information about PSERC can be found at the Center's website: http://www.pserc.org.

### For additional information, contact:

Power Systems Engineering Research Center Arizona State University 527 Engineering Research Center Tempe, Arizona 85287-5706

Phone: 480-965-1643 Fax: 480-965-0745

#### **Notice Concerning Copyright Material**

PSERC members are given permission to copy without fee all or part of this publication for internal use if appropriate attribution is given to this document as the source material. This report is available for downloading from the PSERC website.

© 2013 Washington State University and Georgia Institute of Technology All rights reserved.

# Acknowledgements

This is the final report for the Power Systems Engineering Research Center (PSERC) research project titled "Testing and Validation of Phasor Measurement Based Devices and Algorithms" (project S -45). We express our appreciation for the support provided by PSERC's industry members and by the National Science Foundation under the Industry / University Cooperative Research Center program.

We wish to thank our industry advisors for their support and help: Jeff Fleeman (American Electric Power), Evangelos Farantatos (Electric Power Research Institute), Floyd Galvan (Entergy), Jim Kleitsch (American Transmission Company), Xiaochuan Luo (ISO New England), Bill Middaugh (Tri-state Generation and Transmission), Reynaldo Nuqui (ABB), George Stefopoulos (New York Power Authority), and Sanjoy Sarawgi (American Electric Power).

Special thanks to Southern California Edition to provide internship opportunity related to PMU performance testing to Saugata Biswas. We would also like to thank graduate students Jeong Kim and Hyojong Lee as well as an undergraduate student Rory Beckstorm at Washington State University for their help in PMU and PDC testing. Additionally, we are grateful to Schweitzer Engineering Lab, General Electric, ALSTOM, ERLphase, PONOVO and RTDS, Inc. for their support.

# **Executive Summary**

For upgrading the traditional electric power system to a smart power grid, it is essential to make several enhancements at various levels of operation and control, which includes the integration of Intelligent Electronic Devices (IEDs), synchrophasor devices, advanced communication infrastructure and efficient monitoring and controlling algorithms that would make optimum use of these devices. The event of August 14, 2003 blackout in the north eastern United States and parts of Canada that affected almost 50 million people emphasized the need for real time situational awareness, and thus advocated the use of synchrophasor devices in the power system. PMUs enable the wide area visualization of a power system in real time by capturing high speed time-stamped snapshots in the form of voltage and current phasors, frequency and rate of change of frequency at the rate of up to 120 frames/second. This kind of "time stamping" allows the measurements from different geographical locations to be time-aligned or "synchronized", thus providing a precise and comprehensive view of the entire system. Synchrophasor technology enables a good indication of the status or condition of power grid in real time. However, before putting the smart devices and algorithms in use in the actual power grid, it is of utmost importance to test and validate their capabilities as well as their accuracy.

The motive is to ensure high accuracy of measurements from synchrophasor devices and the validation of developed algorithms utilizing synchrophasors, under different operating scenarios of the power system. This research project report mainly focuses on following goals, (a) testing and validation of synchrophasor devices; b) testing of phasor based voltage stability and state estimation applications utilizing a real time hardware-in-the-loop (HIL) test bed; and (c) utilization of PMUs for advanced protection schemes with emphasis on dynamic protection algorithms for transformers.

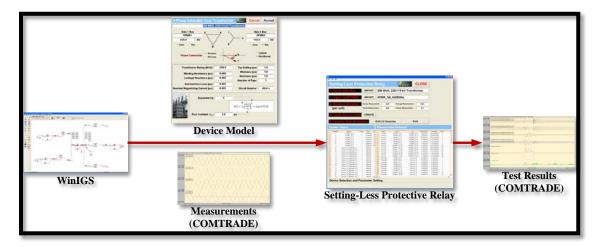

To achieve these goals, the testing facility based on Real Time Digital Simulator (RTDS) at Washington State University (WSU) and WinIGS-T at Georgia Institute of Technology (GIT) were both upgraded to perform testing of synchrophasor devices and applications. For synchrophasor device testing, test systems and also library of test conditions were developed to simulate system scenarios as specified in IEEE C37.118.1 standard. Testing for number of phasor measurement units (PMUs) have been performed against modeled standard PMU. Testing for software and hardware phasor data concentrators (PDCs) have been also performed against limited number of performance criterion. For real time testing and validation of phasor based applications, we focused on voltage stability, state estimators and dynamic protection algorithms for transformers. These applications were simulated in lab environment for some example algorithms to check performance and find potential problems before installing in industry grade power system.

#### **Synchrophasor Device Testing**

Test conditions for PMU's include a) nominal and off-nominal frequency; and b) with and without harmonics, under balanced steady state conditions while magnitude, phase angle and frequency are changed within ranges as specified in the IEEE C37.118.1 standard. For dynamic testing, test conditions include, a) magnitude, angle and frequency

step change; b) frequency ramp change; and c) amplitude, phase and frequency modulation.

The tests reveal that the performance of the different PMUs tested in lab are excellent under steady state conditions and near nominal frequency. The tested PMUs meet the IEEE Standard permissible error of total vector error. However under dynamic and off nominal frequency there is great variability among the various manufacturers and the errors can be quite high. All performance data do not identify the specific device tested. Also, total vector error (TVE) for current is generally higher than voltage TVE and TVE is not the same for each phase. Frequency error (FE) and rate of change in frequency (ROCOF) error (RFE) is within limits for most of the cases. For dynamic testing example of one specific PMU, magnitude step change and angle step change meets the requirement of response time and peak overshoot but not the delay time. For frequency step change, requirements for frequency response time and peak overshoot are met but not the ROCOF response time and delay time. For, frequency ramp change, requirements are not met for FE and RFE. For, amplitude phase and frequency modulation test, PMU fails all performance criterion testing.

Test results for PDC show that the tested PDCs shows satisfactory response in aligning data and data validation test was also successful for different durations and reporting rate of data streaming, collection and archival. There is no data loss, if PMU directly streams data to a PDC without going through a complex communication network. However, when the PMU sends data to the PDC via communication networks, there is considerable data loss. Data latency, data rate conversion, format conversion, phase/ magnitude compensation were found satisfactory for tested PDC's.

#### **Synchrophasor Application Testing**

The test bed was modified to perform real time testing of voltage stability algorithms using real time controllers and real time digital simulators. Voltage stability algorithm tested in lab shows performance as expected for line outages and change in loading conditions. State estimation algorithm is dynamic and perform very well with transformer inrush current, over-excitation and with fault conditions.

The setting-less protection approach based on dynamic state estimation for the 3-phase transformer has been proven to be a reliable method to protect the transformer against internal faults. It was shown that the relay does not trip during normal operating conditions or faults outside the protection zone. On the other hand, a trip is decided during the internal fault. The simulation results verify the theoretical analysis. The computation time needed is within the requirements of the data acquisition scheme.

Outcomes of this project include (a) Set of standard accuracy and performance tests for PMUs; (b) An enhanced test bed to demonstrate operation of phasor devices for research/educational purposes; (c) Evaluation of PMU based applications including voltage stability and state estimation in real time; and (d) Better dynamic protection algorithm for transformer.

Performance results reported here for PMU and PDC can be used to guide evolution of the standards and to provide insight for manufacturer. Test results also shows need for additional algorithms to filter out bad data for applications related to transients and dynamics as well as real time control. Dynamic protection algorithms for transformer protection can be incorporated in new relays with PMU capability.

#### **Project Publications:**

- [1]. Saugata S. Biswas, Jeong Hun Kim and Anurag K. Srivastava, "Development of a Smart Grid Test bed and Applications in PMU and PDC Testing," in *North American Power Symposium (NAPS)*, *Urbana, IL*, September 2012.

- [2]. Saugata S. Biswas and Anurag K. Srivastava, "Real time Testing and Validation of Smart Grid Devices and Algorithms," in *IEEE PES General Meeting*, Vancouver, CA, July 2013.

- [3]. Saugata S. Biswas and Anurag K Srivastava, "A Novel Method for Distributed Real Time Voltage Stability Monitoring Using Synchrophasor Measurements", IREP Symposium, Rethymnon, Crete, Greece, June 2013.

- [4]. Saugata S Biswas and Anurag K Srivastava, "A fast Algorithm for Voltage Stability Monitoring of Power Systems with Consideration of Load Models", IEEE IAS Meeting, Orlando, FL, October, 2013.

- [5]. Saugata S. Biswas, Ceeman B. Vellaithurai and Anurag K. Srivastava, "Development and Real Time Implementation of a Synchrophasor based Fast Voltage Stability Monitoring Algorithm with Consideration of Load Models," submitted to IEEE Transactions for Industrial Applications.

- [6]. Sakis Meliopoulos, George Cokkinides, Zhenyu Tan, Sungyun Choi, Yonghee Lee and Paul Myrda, "Setting-less Protection: Feasibility Study", proceedings of HICSS 2013, Maui, HI, January 2013

- [7]. A. P. Meliopoulos, E. Polymeneas, Zhenyu Tan, Renke Huang, and Dongbo Zhao, "Advanced Distribution Management System", *IEEE Transactions on Smart Grid*, accepted.

- [8]. Sakis Meliopoulos, G. J. Cokkinides, S. Grijalva, R. Huang, E. Polymeneas, Paul Myrda, Evangelos Farantatos, Mel Gehrs, "Integration & Automation: From Protection to Advanced Energy Management Systems", IREP Symposium, Rethymnon, Crete, Greece, June 2013.

#### **Student Theses:**

- [1]. Saugata Biswas, Development and validation of real time monitoring and control algorithms for power system, Ph.D. thesis, Washington State University, May 2014.

- [2]. Yonghee Lee, Comprehensive Protection Schemes of a Microgrid and Distribution Systems, Ph.D. thesis, Georgia Institute of Technology, in progress.

- [3]. Stefan Ntwoku, Dynamic Transformer Protection: a Novel Approach Using State Estimation, Georgia Institute of Technology, August 2012.

# **Table of Contents**

| 1. Introduction                                                         | 1             |

|-------------------------------------------------------------------------|---------------|

| 1.1 Background                                                          | 1             |

| 1.2 Project Objectives and Overview                                     | 1             |

| 1.3 Report Organization                                                 | 2             |

| 2. Synchrophasor Device Testing                                         | 3             |

| 2.1 RTDS Based Testing Facility                                         | 3             |

| 2.2.1 Description                                                       | 3             |

| 2.2.2 PMU Testing                                                       | 4             |

| 2.2.3 PDC Testing                                                       | 26            |

| 2.2 WinIGS-T based Testing Facility                                     | 35            |

| 2.2.3 Description                                                       | 35            |

| 2.2.4 PMU Testing                                                       | 36            |

| 3 Validation and Testing of Synchrophasor Applications                  | 52            |

| 3.1 Voltage Stability Algorithms Based on Synchrophasor Data            | 52            |

| 3.1.1 Introduction to Voltage Stability                                 | 52            |

| 3.1.2 Testbed for performing online simulation of voltage stability a   | algorithms 53 |

| 3.1.3 Performance of online simulations of voltage stability algorithms | nm58          |

| 3.1.4 Conclusion from Test Results                                      | 66            |

| 3.2 Comparing State Estimation Algorithms Using Synchrophasor Da        | ata 67        |

| 3.3 Dynamic State Estimation Based Protection Algorithms for Transf     | Formers 70    |

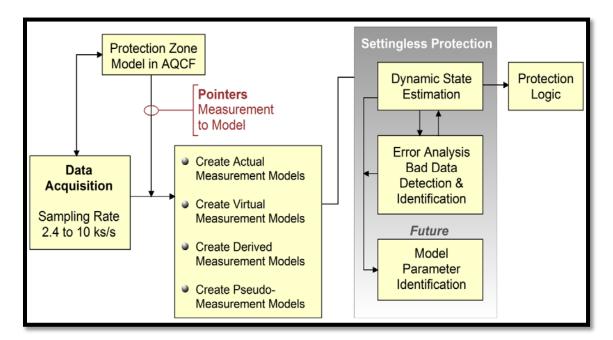

| 3.3.1 Description of the approach                                       | 70            |

| 3.3.2 Transformer Setting-less Protection Approach Description          | 72            |

| 3.3.3 Protection Logic                                                  | 81            |

| 3.3.4 Transformer Setting-less protection results                       | 83            |

| 3.3.5 Conclusions on DSE Based Transformer Protection                   | 99            |

| 4 Conclusions and Future Research Direction                             | 100           |

| 4.1 Conclusions                                                         | 100           |

| 4.2 Future Research Directions                                          | 101           |

| References                                                              | 103           |

# **List of Figures**

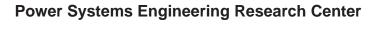

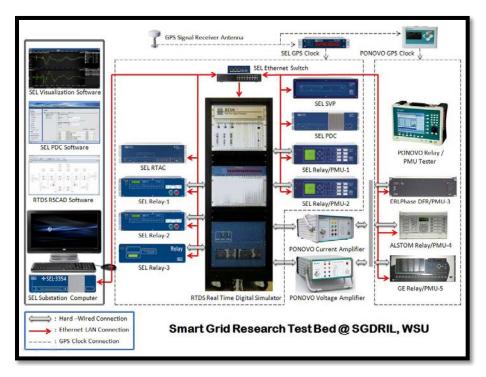

| Figure 2.1: Test bed at Washington State University                              | 3  |

|----------------------------------------------------------------------------------|----|

| Figure 2.2: Example of a draft case for simulating a PMU test condition          | 5  |

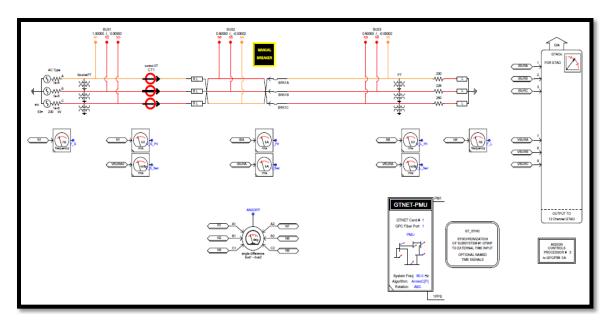

| Figure 2.3: Example of RSCAD run case for obtaining test measurements            | 6  |

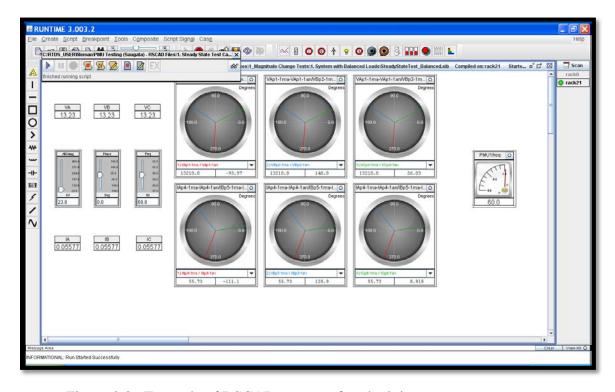

| Figure 2.4: Example of data archival in software PDC                             | 7  |

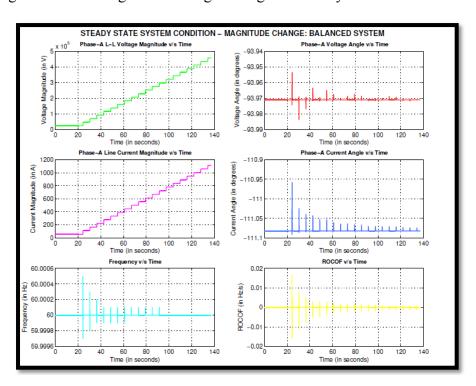

| Figure 2.5: Test conditions for magnitude change (balanced, nominal)             | 9  |

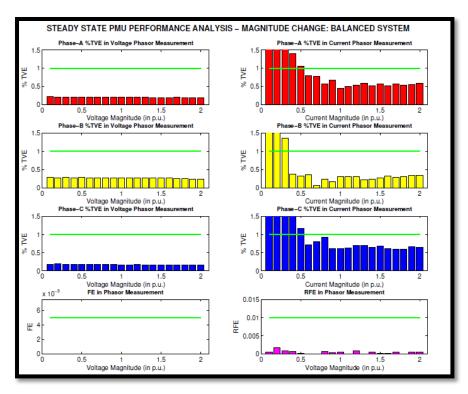

| Figure 2.6: Error analysis for magnitude change (balanced, nominal)              | 10 |

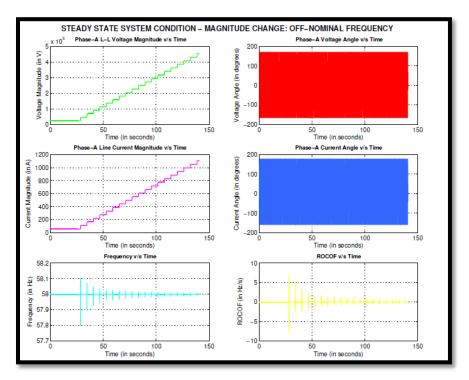

| Figure 2.7: Test conditions for magnitude change (balanced, off-nominal)         | 11 |

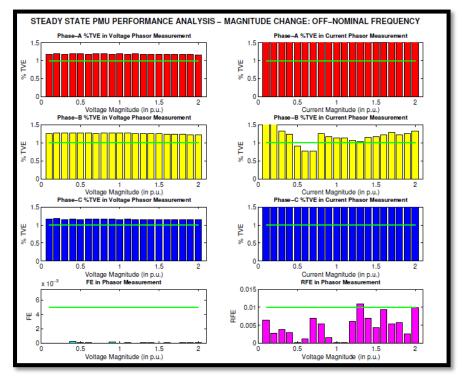

| Figure 2.8: Error analysis for magnitude change (balanced, off-nominal)          | 11 |

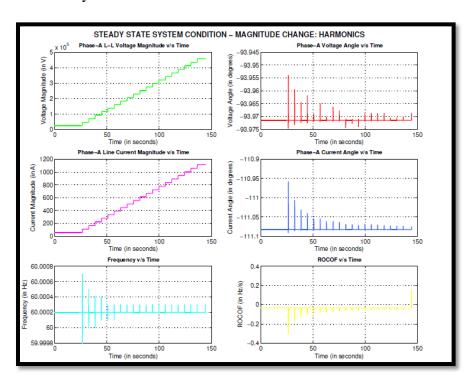

| Figure 2.9: Test conditions for magnitude change (harmonics, nominal)            | 12 |

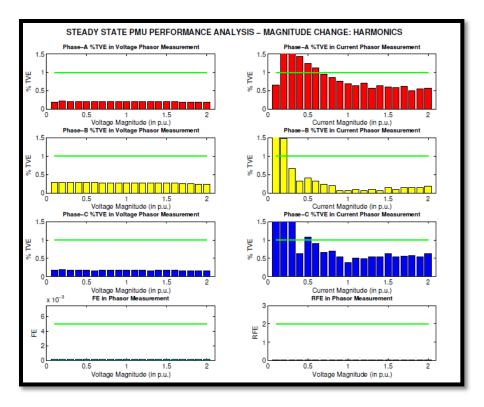

| Figure 2.10: Error analysis for magnitude change (harmonics, nominal)            | 13 |

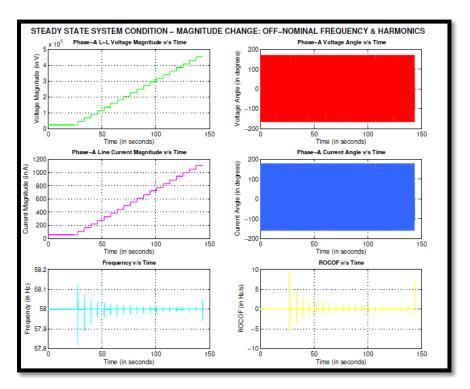

| Figure 2.11: Test conditions for magnitude change (harmonics, off-nominal)       | 14 |

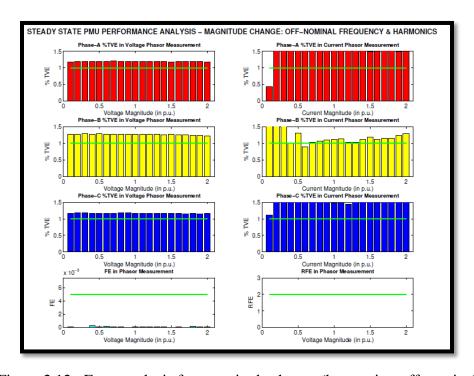

| Figure 2.12: Error analysis for magnitude change (harmonics, off-nominal)        | 14 |

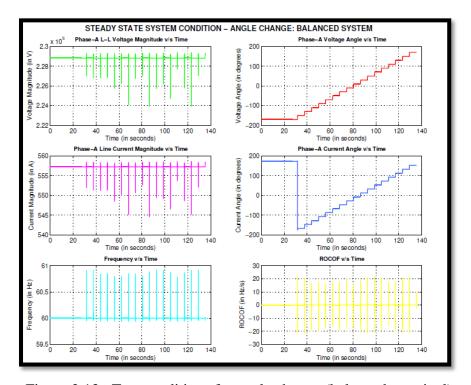

| Figure 2.13: Test conditions for angle change (balanced, nominal)                | 15 |

| Figure 2.14: Error analysis for angle change (balanced, nominal)                 | 16 |

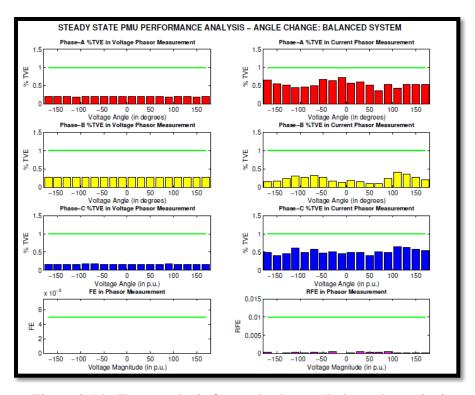

| Figure 2.15: Test conditions for angle change (harmonics, nominal)               | 17 |

| Figure 2.16: Error analysis for angle change (harmonics, nominal)                | 18 |

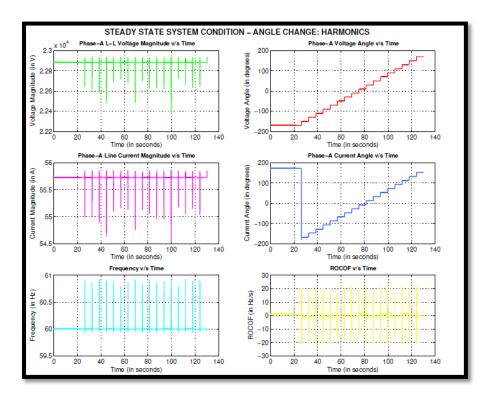

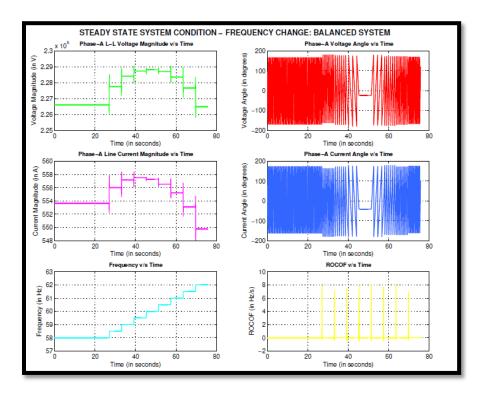

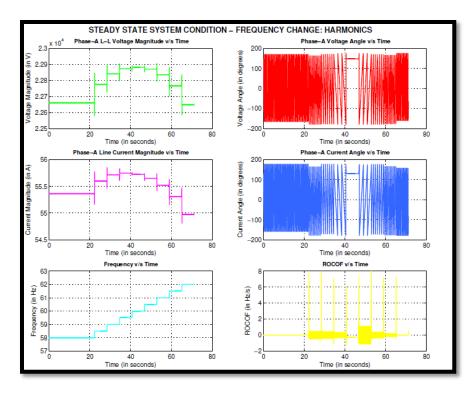

| Figure 2.17: Test conditions for frequency change (balanced)                     | 18 |

| Figure 2.18: Error analysis for frequency change (balanced)                      | 19 |

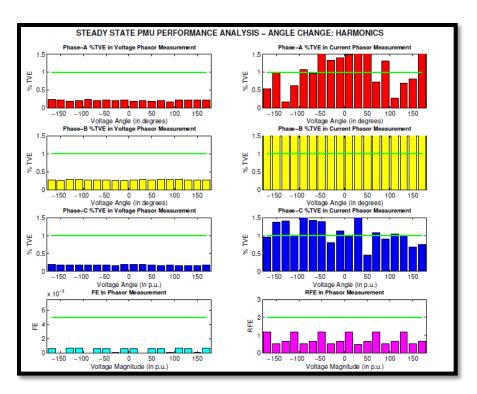

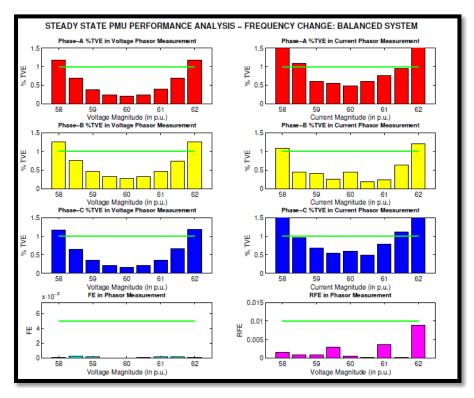

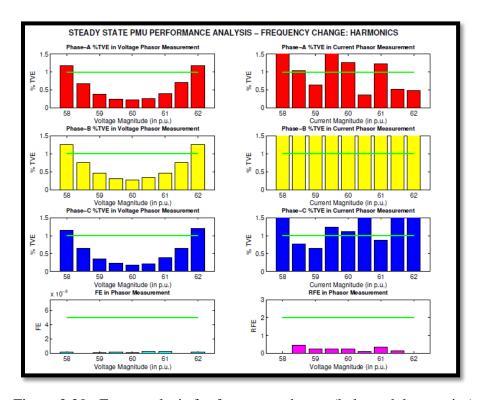

| Figure 2.19: Test conditions for frequency change (balanced, harmonics)          | 20 |

| Figure 2.20: Error analysis for frequency change (balanced, harmonics)           | 20 |

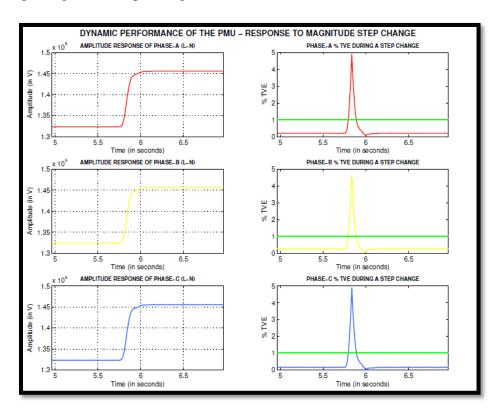

| Figure 2.21: Response during step change in voltage magnitude                    | 21 |

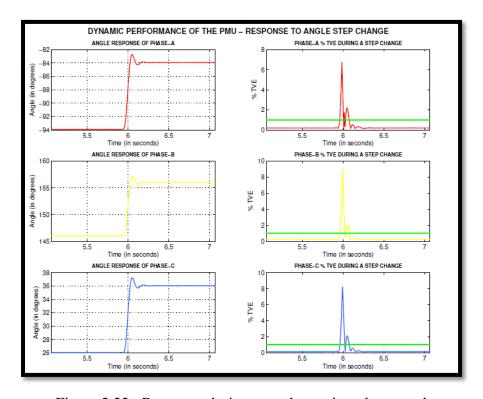

| Figure 2.22: Response during step change in voltage angle                        | 22 |

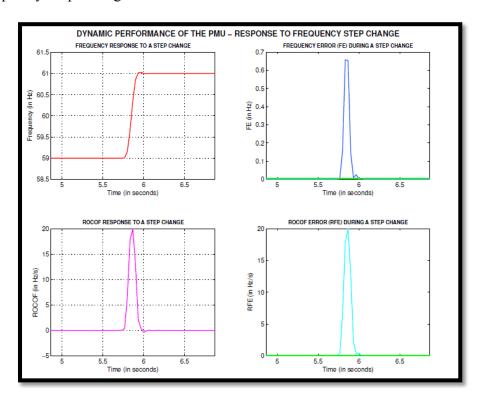

| Figure 2.23: Response during step change in frequency                            | 23 |

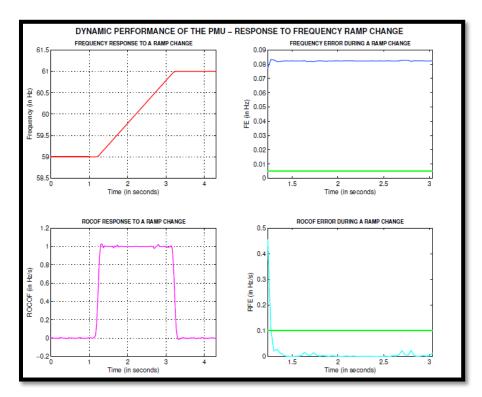

| Figure 2.24: Response during ramp change in frequency                            | 24 |

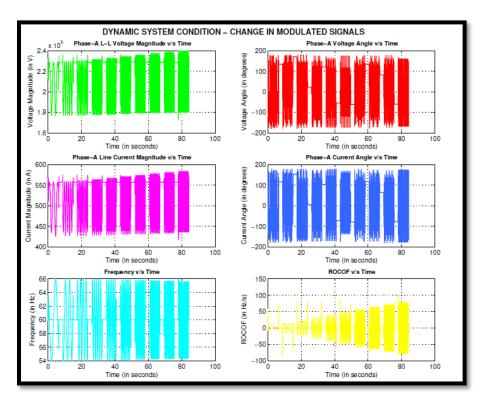

| Figure 2.25: Dynamic test conditions for change in modulated signal              | 25 |

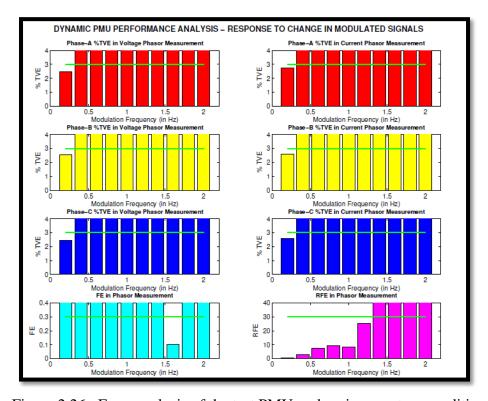

| Figure 2.26: Error analysis of the test PMU under given system condition         | 25 |

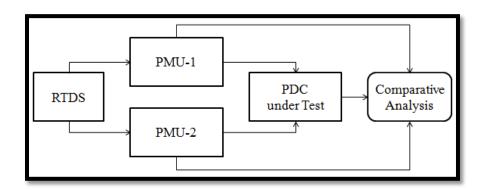

| Figure 2.27: Test bed for testing PDCs without communication modeling            | 30 |

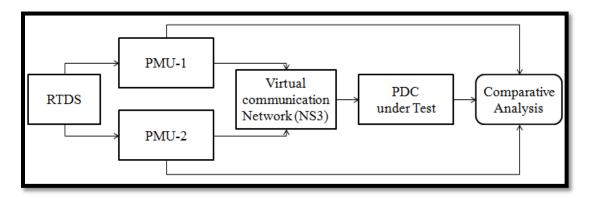

| Figure 2.28: Test bed for testing PDCs with communication model                  | 30 |

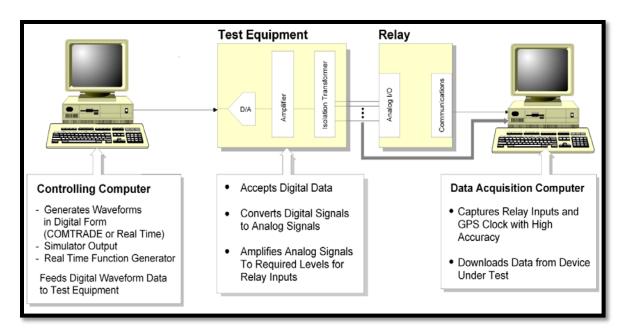

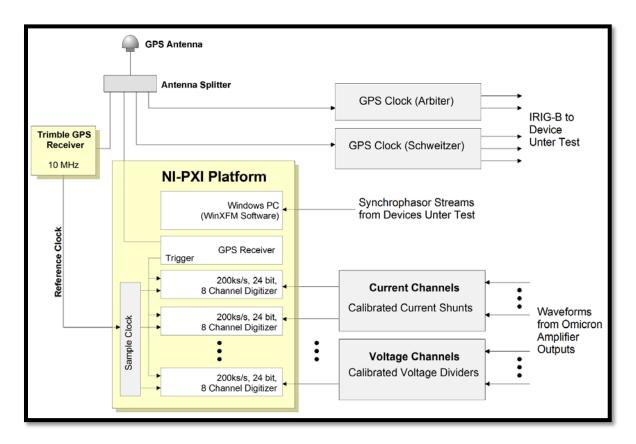

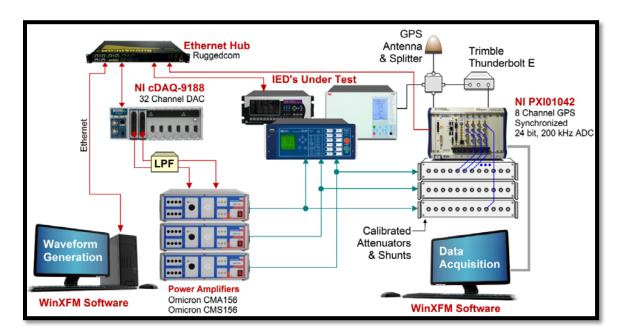

| Figure 2.29: Hardware configuration for testing GPS-synchronized IEDs/ PMU       | 37 |

| Figure 2.30: Schematic of software architecture for GPS-synchronized IED testing | 38 |

| Figure 2.31: Data acquisition system block diagram                               | 38 |

| Figure 2.32: Laboratory setup for PMU testing                                      | . 39 |

|------------------------------------------------------------------------------------|------|

| Figure 2.33: Laboratory setup for PMU testing                                      | . 39 |

| Figure 2.34: Illustration of Total Vector Error (TVE)                              | . 40 |

| Figure 2.35: Illustration of timing error measurement                              | . 41 |

| Figure 2.36: Illustration of phase error measurement                               | . 43 |

| Figure 2.37: Test B-1: Frequency ramp, no harmonics                                | . 48 |

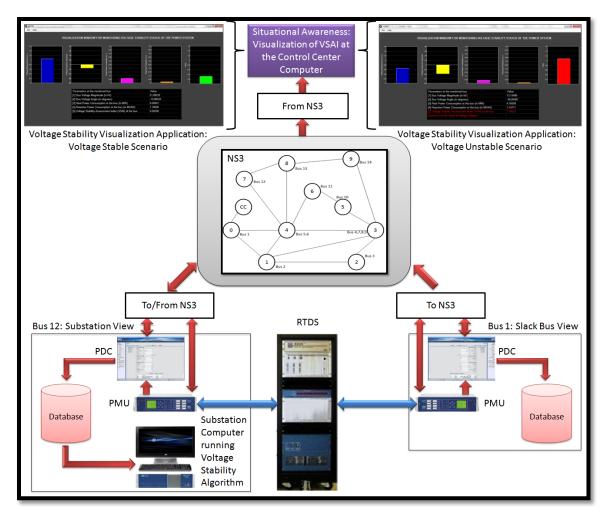

| Figure 3.1: Smart grid test bed for simulation of voltage stability algorithm      | . 57 |

| Figure 3.2: Functional block diagram for simulation of voltage stability algorithm | . 59 |

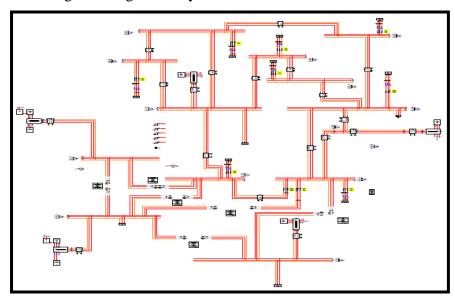

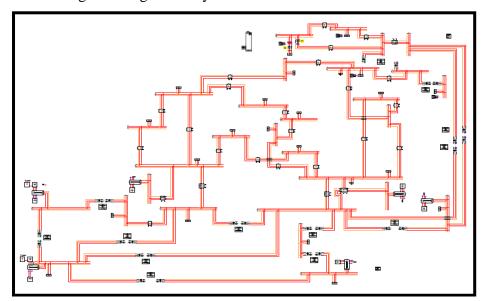

| Figure 3.3: IEEE-14 bus test case modeled in RSCAD for real time simulation        | . 60 |

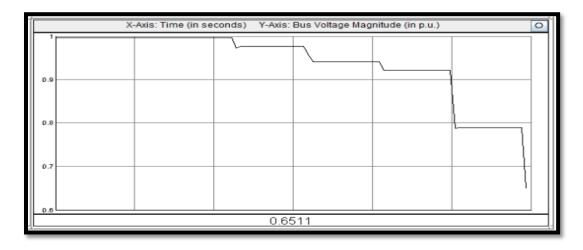

| Figure 3.4: RSCAD voltage magnitude changes at Bus-12 for IEEE 14 bus              | . 61 |

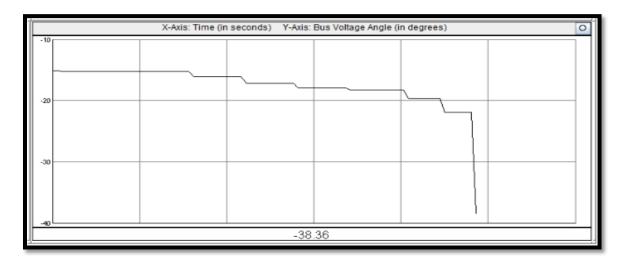

| Figure 3.5: RSCAD showing angle changes at Bus-12 for IEEE 14 bus                  | . 61 |

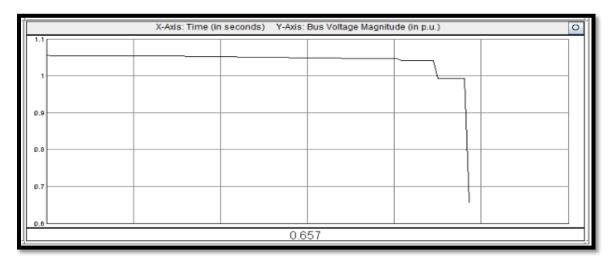

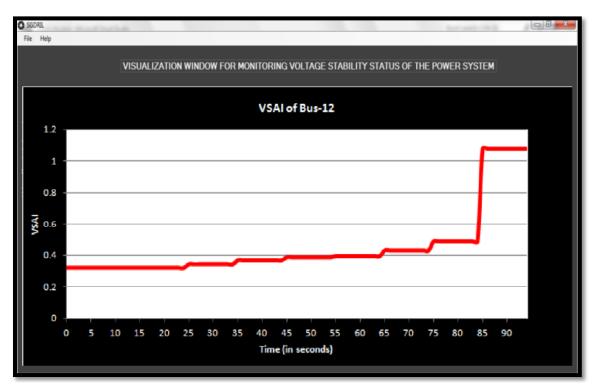

| Figure 3.6: VSAI leading to voltage collapse from $t=0$ s to $t=85$ s              | . 62 |

| Figure 3.7: IEEE-30 bus test case modeled in RSCAD for real time simulation        | . 63 |

| Figure 3.8: RSCAD showing voltage magnitude changes at bus-30 for IEEE 30 bus      | . 64 |

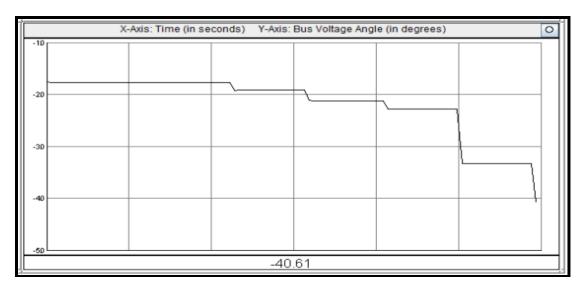

| Figure 3.9: RSCAD showing angle changes at bus-30 for IEEE 30 bus                  | . 65 |

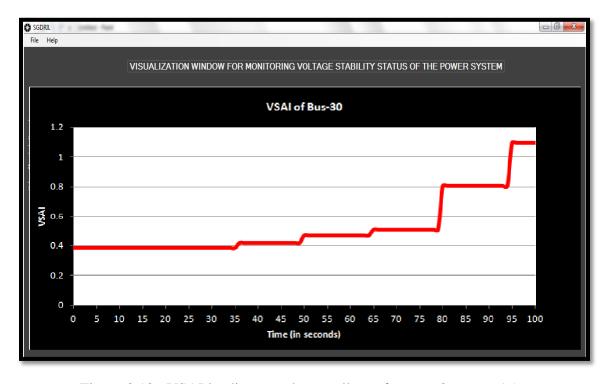

| Figure 3.10: VSAI leading to voltage collapse from $t = 0$ s to $t = 95$ s         | . 65 |

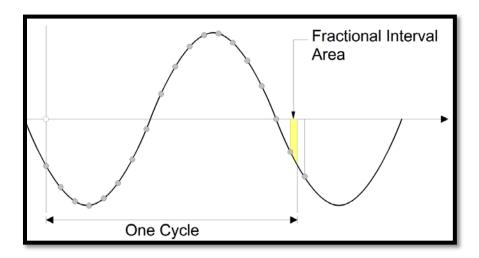

| Figure 3.11: Fractional sample integration                                         | . 68 |

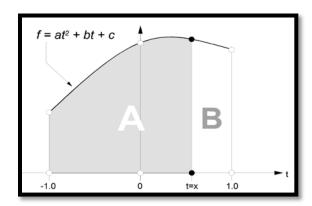

| Figure 3.12: Quadratic approximation of a function from three successive samples   | . 69 |

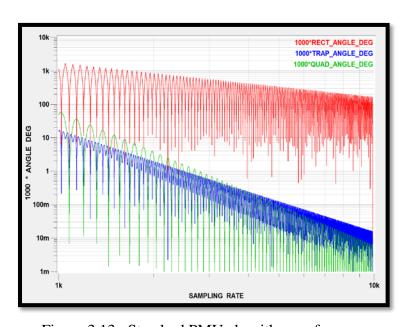

| Figure 3.13: Standard PMU algorithm performance                                    | . 69 |

| Figure 3.14: Architecture of the dynamic state estimation based protective relay   | . 70 |

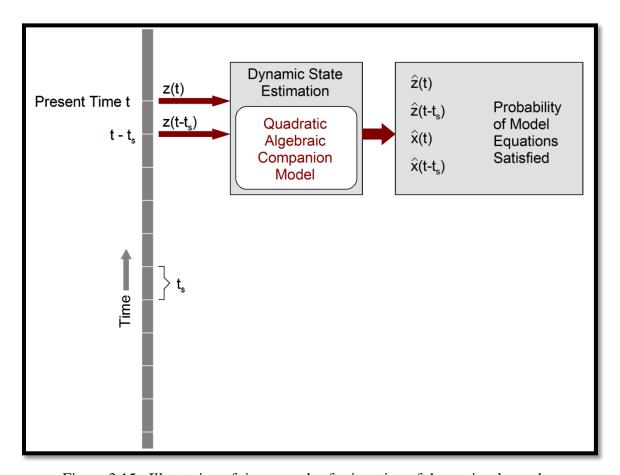

| Figure 3.15: Illustration of time samples for iteration of the setting-less relay  | . 71 |

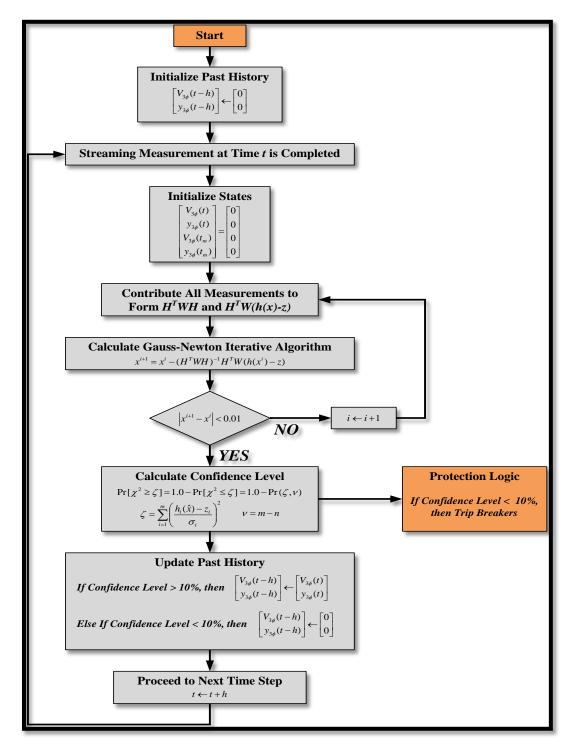

| Figure 3.16: Overall algorithm of state estimation                                 | . 82 |

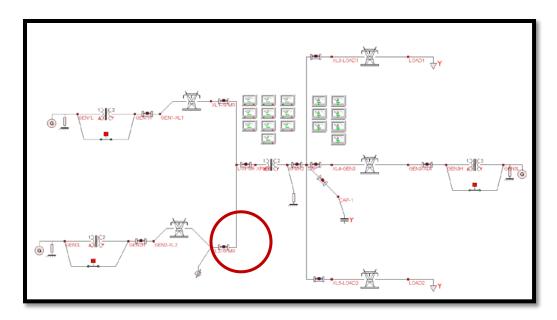

| Figure 3.17: Test scheme for verifying the proposed protection method              | . 83 |

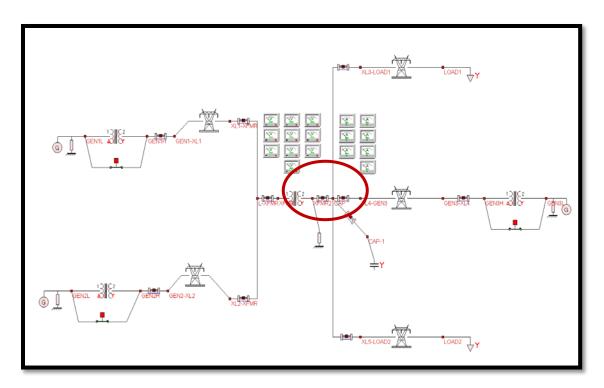

| Figure 3.18: Test system for the setting-less protection                           | . 84 |

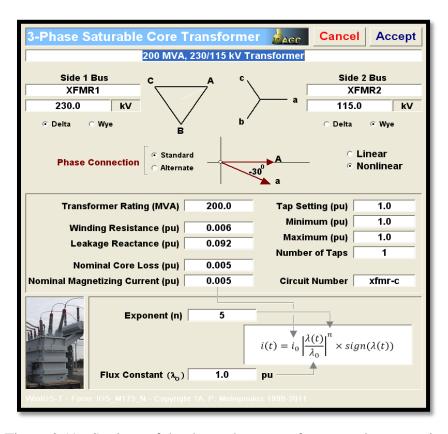

| Figure 3.19: Settings of the three-phase transformer under protection              | . 84 |

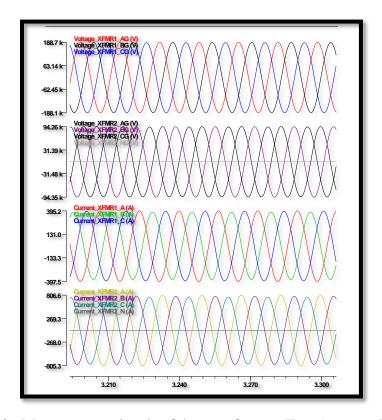

| Figure 3.20: Measurement signals of the transformer (Test A: normal operation)     | . 85 |

| Figure 3.21: Measurement signals of the transformer (Test B: energization)         | . 86 |

| Figure 3.22: Measurement signals of the transformer (Test C: overexcitation)       | . 87 |

| Figure 3.23: Fault location in the test system (test D: through fault)             | . 88 |

| Figure 3.24: Measurement signals of the transformer (Test D: through fault)        | . 88 |

| Figure 3.25: Fault location in the test system (Test E: internal fault)            | . 89 |

| Figure 3.26: Measurement signals of the transformer (Test E: internal fault)       | . 89 |

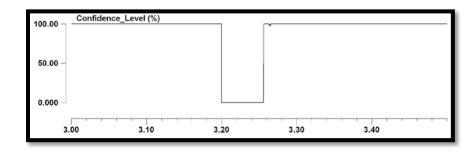

| Figure 3.27: Confidence level of the DSE (Test A: normal operation)                | . 90 |

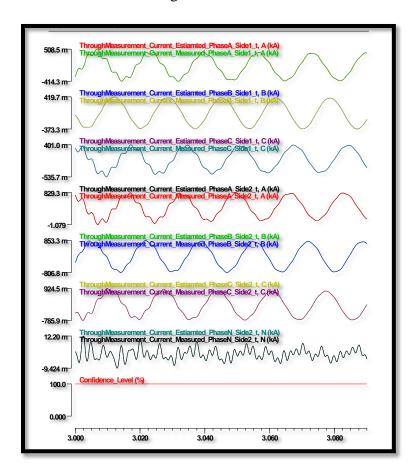

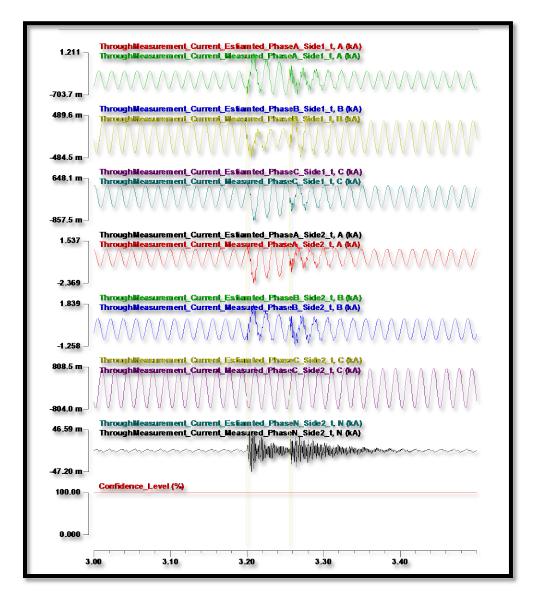

| Figure 3.28: | Current measurements, estimated values, and confidence level (Test A) 90         |

|--------------|----------------------------------------------------------------------------------|

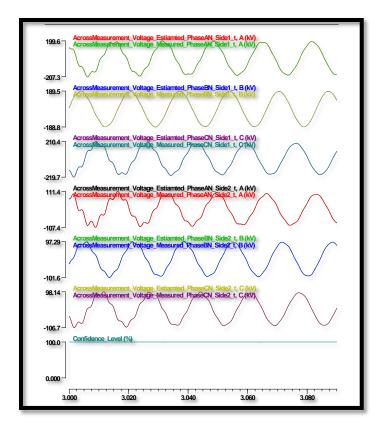

| Figure 3.29: | Voltage measurements, estimated values, and confidence level (Test A) 91         |

| Figure 3.30: | Confidence level of the DSE (Test B: transformer energization)                   |

| Figure 3.31: | Current measurements, estimated values, and confidence level (Test B) $\dots$ 92 |

| Figure 3.32: | Voltage measurements, estimated values, and confidence level (Test B) 93         |

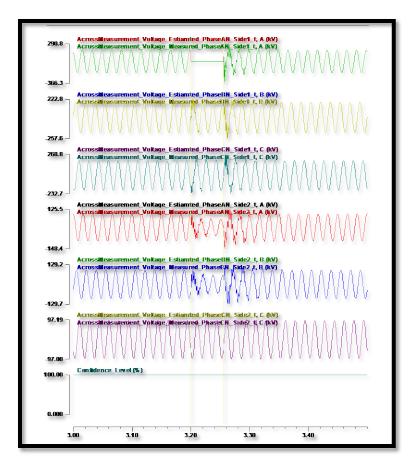

| Figure 3.33: | Confidence level of the DSE (Test C: transformer overexcitation)94               |

| Figure 3.34: | Current measurements, estimated values, and confidence level (Test C) $\dots$ 94 |

| Figure 3.35: | Voltage measurements, estimated values, and confidence level (Test C) 95         |

| Figure 3.36: | Confidence level of the DSE (Test D: through fault)                              |

| Figure 3.37: | Current measurements, estimated values, and confidence level (Test D) 96         |

| Figure 3.38: | Voltage measurements, estimated values, and confidence level (Test D) 97         |

| Figure 3.39: | Confidence level of the DSE (Test E: internal fault)                             |

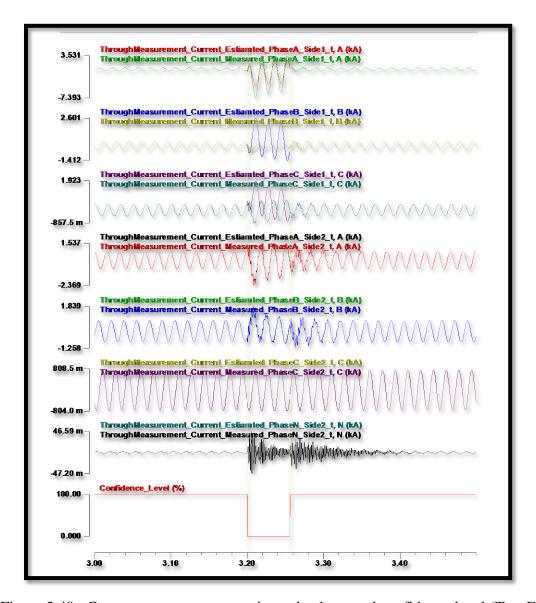

| Figure 3.40: | Current measurements, estimated values, and confidence level (Test E) $\dots$ 98 |

| Figure 3.41: | Voltage measurements, estimated values, and confidence level (Test E) 99         |

# **List of Tables**

| Table 2.1: Library of test conditions for PMU testing                              | 5  |

|------------------------------------------------------------------------------------|----|

| Table 2.2: Test results for response to magnitude step change                      | 22 |

| Table 2.3: Test results for response to angle step change                          | 22 |

| Table 2.4: Test results for response to frequency step change                      | 23 |

| Table 2.5: Test results for response to frequency ramp change                      | 24 |

| Table 2.6: Library of PDC tests                                                    | 29 |

| Table 2.7: Test results for time alignment (rate = 30 frames / second)             | 31 |

| Table 2.8: Test results for time alignment (rate = 60 frames / second)             | 31 |

| Table 2.9: Test results for data validation (rate = 30 frames / second)            | 31 |

| Table 2.10: Test results for data validation (date = 60 frames / second)           | 32 |

| Table 2.11: Test results for data loss (rate = 30 frames / second)                 | 32 |

| Table 2.12: Test results for data loss (rate = 60 frames / second)                 | 32 |

| Table 2.13: Test results for data loss with network (rate = 60 frames / second)    | 33 |

| Table 2.14: Test results for data latency                                          | 33 |

| Table 2.15: Test results for report rate conversion (60 to 30)                     | 33 |

| Table 2.16: Test results for report rate conversion (30 to 60)                     | 34 |

| Table 2.17: Test results for format & coordinate conversion (polar to rectangular) | 34 |

| Table 2.18: Test results for format & coordinate conversion (rectangular to polar) | 34 |

| Table 2.19: Phase angle adjustment (+5 degrees)                                    | 34 |

| Table 2.20: Phase angle adjustment (-5 degrees)                                    | 35 |

| Table 2.21: Magnitude adjustment (+5%)                                             | 35 |

| Table 2.22: Magnitude adjustment (-5%)                                             | 35 |

| Table 2.23: Test conditions for steady state performance                           | 45 |

| Table 2.24: Test conditions for frequency ramp test                                | 46 |

| Table 2.25: Test conditions for voltage magnitude test                             | 46 |

| Table 2.26: Test conditions for voltage magnitude step change                      | 47 |

| Table 2.27: Test conditions for current magnitude                                  | 47 |

| Table 2.28: Test conditions for voltage and current imbalance tests                | 48 |

| Table 2.29: Performance evaluation - individual phase analysis - test signals A    | 49 |

| Table 2.30: Performance evaluation - positive sequence - test signals A            | 50 |

| Table 2.31: Performance evaluation - individual phase analysis - test signals B    | 51 |

| Table 2.32: Performance evaluation - positive sequence - test signals B          | . 51 |

|----------------------------------------------------------------------------------|------|

| Table 3.1: Series of events leading to voltage collapse in IEEE-14 bus test case | . 60 |

| Table 3.2: VSAI in real time for each event leading to voltage collapse          | . 62 |

| Table 3.3: Propagation delays between substations and control center             | . 63 |

| Table 3.4: Series of events leading to voltage collapse in IEEE-30 bus test case | . 64 |

| Table 3.5: VSAI computed in real time for each event leading to voltage collapse | . 66 |

| Table 3.6: Propagation delays between substations and control center for 30 bus  | . 66 |

| Table 3.7: Phase error at sampling rate of 8 KHz                                 | . 69 |

| Table 3.8: All state variables of the three-phase transformer $(n = 5)$          | . 73 |

| Table 3.9: Actual across measurements for the three-phase transformer            | . 76 |

| Table 3.10: Actual through measurements for the three-phase transformer          | . 77 |

| Table 3.11: Virtual measurements for the three-phase transformer                 | . 78 |

| Table 3.12: Pseudo measurements for the three-phase transformer                  | . 80 |

| Table 3.13: Transformer parameters (identical at all phases)                     | . 85 |

## 1. Introduction

### 1.1 Background

Implementation of the future smart grid requires adopting number of new technologies including integration of phasor based devices and new algorithms to utilize synchrophasor data for various applications. These newly developed phasor based applications need to be validated before actual implementation. In order to properly evaluate the applications, it is important to characterize the phasor measurement units (PMUs) and the quality of data obtained with the PMUs. Testing of phasor based devices including PMUs and phasor data concentrators (PDCs) for technical performance are required before installing in real world application. Utilities need to assure the reliable operation of PMUs with high data quality before they will invest heavily in them. PMU data quality is critical especially for control applications. The updated Synchrophasor standard IEEE C37.118.1-2011 (released in 2011) defines the requirements for the PMU measurements in terms of the steady state performance evaluation quantities like Total Vector Error (TVE), Frequency Error (FE) and Rate of change of Frequency Error (RFE), and dynamic evaluation quantities like peak overshoot, response time and delay time [1, 2]. The standard specifies test conditions that include various ranges of signal frequency, magnitude and phase angle, as well as levels of harmonic distortion. North American Synchro Phasor Initiative (NASPI) [3] has also addressed the issue of PMU testing to help with developing technical guidelines and educational documents. There are other parallel efforts by researchers, but PMU applications and devices have been evolving over the years and need to be tested with new developments.

#### 1.2 Project Objectives and Overview

This research project mainly focuses on (a) testing of phasor devices like PMUs and PDCs; (b) testing and validation of phasor based voltage stability and state estimation applications utilizing an existing real time hardware-in-the-loop (HIL) test bed; and (c) utilization of PMUs for advanced protection schemes with emphasis on dynamic protection algorithms for transformers.

Two proposed test beds have been utilized, one based on the Real Time Digital Simulator (RTDS) at WSU [4, 5] and another based on a digital simulator (WinIGS-T) at GIT. Both test beds utilize additional hardware and software tools including Phasor Measurement Units (PMUs), amplifiers, Synchrophasor Vector Processor (SVP), Phasor Data Concentrators (PDC) and Historians.

Voltage stability and state estimation algorithms based on PMU data have been addressed in several publications but there is need for real time validation before implementation. Dynamic protection algorithms are in their infancy - yet they offer great promise to provide robust, reliable protection schemes for the most difficult protection problems. The use of PMUs for dynamic protection algorithms for transformer protection has been investigated in this project. Transformer protection is the best candidate to test dynamic

protection algorithms since inrush currents in transformers have been known to impose compromises in differential transformer protection. For instance, the many excellent schemes to deal with inrush currents in transformer protection: the algorithms and hardware for identifying inrush currents are not fully reliable or accurate and as a result the settings are normally desensitized, protection action is delayed and transformers are subjected to abnormal conditions longer than necessary. It is generally accepted that dynamic protection algorithms have the capacity to provide more robust, highly selective and reliable algorithms.

This project provides several potential benefits including (a) Better dynamic protection algorithm for transformer; (b) Set of standard accuracy and performance tests for PMUs and a guide for PMU real time applications resulting in cost reduction and verifiable operational performance; (c) An enhanced test bed to demonstrate operation of phasor devices for educational purposes; and (d) Evaluation of PMU based applications including voltage stability and state estimation in real time. Improved test bed can be used for educational/research purpose.

## 1.3 Report Organization

This report has been organized in four sections. Section 1 provides introduction, project objectives and overview of the problem. Section 2 provides details for testing of phasor measurement devices and phasor data concentrator using the enhanced test bed at WSU and GIT. Section 3 presents test results for testing and validation of three different phasor applications for voltage stability, state estimation and dynamic protection. Section 4 concludes the report.

# 2. Synchrophasor Device Testing

### 2.1 RTDS Based Testing Facility

## 2.2.1 Description

Real Time Digital Simulator (RTDS) is a power system simulator that simulates a power system built in RSCAD user interface software in real time. The RTDS works on the parallel processing technology of digital signal processors and executes the program developed on its processors. The RTDS not only calculates and shows the electrical output values in the runtime software, but also produces scaled output signals (digital as well as analog) through the output interface cards incorporated into its system.

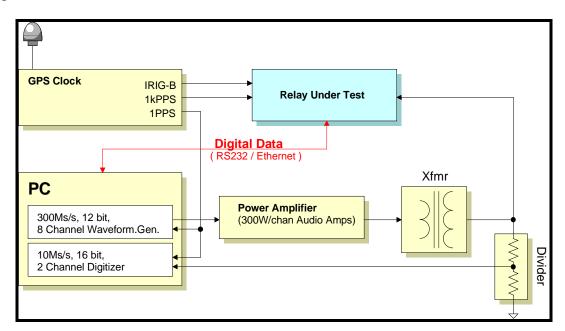

Figure 2.1: Test bed at Washington State University

The RTDS facility installed at the Smart Grid Demonstration & Research Investigation Lab (SGDRIL), WSU, consists of one rack with three Giga Processor Cards (GPCs) and two PB5 Cards for processing required computations in real time. Other components include: a) One Giga Transceiver Workstation Interface Card (GTWIF) – for interfacing the RSCAD user software with the GPC cards of the RTDS; b) one Giga Transceiver Digital Input Card (GTDI) – for taking in input digital signals from external devices like PMU/ relays; c) one Giga Transceiver Front Panel Interface card (GTFPI) – for taking in

input digital signals and giving out output digital signals from and to hardware devices like relays; d) three Giga Transceiver Analog Output Card (GTAO) – for providing analog output signals to hardware devices like PMUs for measuring electrical quantities; e) one Giga Transceiver Analog Input Card (GTAI) – for taking in analog input signals from hardware devices; f) one Giga Transceiver Network Interface Card (GTNET) – for interfacing a number of different network protocols with the RTDS simulator; and g) one Giga Transceiver Synchronization Card (GTSYNC) – for synchronizing the RTDS simulation time step to an external time reference like the GPS clock. Additionally, test bed consists of number of PMU devices, phasor data concentrators (PDCs), synchrophasor vector processors (SVP), controllers, and amplifiers. Fig. 2.1 shows the lab setup at WSU.

#### 2.2.2 PMU Testing

#### 2.1.2.1 Introduction

PMUs enable the wide area visualization of a power system in real time by capturing high speed time-stamped snapshots in the form of voltage and current phasors, frequency and rate of change of frequency at the rate of 30/60/120 Frames / second [6]. This kind of "time stamping" allows the measurements from different geographical locations to be time-aligned or "synchronized", thus providing a precise and comprehensive view of the entire system. Hence, synchrophasor technology enables a good indication of the status or condition of power grid in real time. However, before putting the smart devices and algorithms in use in the actual power grid, it is of utmost importance to test and validate their capabilities as well as their accuracy. The motive is to ensure high reliability and accuracy of these devices and the developed algorithms, under different operating scenarios of the power system.

#### 2.1.2.2 Library of Test Conditions

IEEE Standard for Synchrophasors C37.118 - 2011 [7] is the latest standard that provide the PMU performance conformance test details. This Standard has been divided into two parts - C37.118.1 and C37.118.2, where the former specifies the tests required for PMU measurement performance conformance, while the latter specifies the tests required for PMU communication performance conformance. In this project, the PMU measurement performance tests have been performed (as mentioned in IEEE C37.118.1). Also additional tests that are not in the present standard have been performed, keeping in mind some of the realistic system conditions in which the PMUs are supposed to operate when deployed in substations. Thus, the specially designed test library performs a comprehensive performance analysis of the PMUs.

The 'library of test conditions' has been created in the RTDS using test case as shown in fig. 2.2. Individual test cases have been created in the RTDS Draft case so as to generate the test signals. The ideal PMU is the GTNET PMU available in the RTDS. The draft case is set up in such a way the test PMU is connected to the same bus as that of the GTNET PMU, so that both the PMUs get the same measurements as their inputs.

Figure 2.2: Example of a draft case for simulating a PMU test condition

Table 2.1: Library of test conditions for PMU testing

| <b>Main Category of</b> | Quantities           | System Conditions during       | PMU Performance    |

|-------------------------|----------------------|--------------------------------|--------------------|

| PMU Testing             | Changed during       | Testing                        | Evaluation         |

| _                       | Testing              | _                              | Parameters         |

| Steady State Tests      | Voltage & Current    | System is balanced             | TVE, FE, RFE       |

|                         | Magnitude            | System is at off-nominal       | TVE, FE, RFE       |

|                         |                      | frequency                      |                    |

|                         |                      | System has harmonics           | TVE, FE, RFE       |

|                         |                      | System is at off-nominal       | TVE, FE, RFE       |

|                         |                      | frequency and has harmonics    |                    |

|                         | Voltage & Current    | System is balanced             | TVE, FE, RFE       |

|                         | Angle                | System has harmonics           | TVE, FE, RFE       |

|                         | Frequency            | System is balanced             | TVE, FE, RFE       |

|                         |                      | System has harmonics           | TVE, FE, RFE       |

| Dynamic Tests           | Voltage Magnitude    | System is balanced, at nominal | Response Time,     |

|                         | Step                 | frequency, without harmonics   | Delay Time,        |

|                         |                      |                                | % Peak Overshoot   |

|                         | Voltage Angle Step   | System is balanced, at nominal | Response Time,     |

|                         |                      | frequency, without harmonics   | Delay Time,        |

|                         |                      |                                | % Peak Overshoot   |

|                         | Frequency Step       | System is balanced, at nominal | Frequency Response |

|                         |                      | frequency, without harmonics   | Time, ROCOF        |

|                         |                      |                                | Response Time,     |

|                         |                      |                                | Delay Time,        |

|                         |                      |                                | % Peak Overshoot   |

|                         | Frequency Ramp       | System is balanced, at nominal | FE, RFE            |

|                         |                      | frequency, without harmonics   |                    |

|                         | Amplitude, Phase &   | System is balanced, at nominal | TVE, FE, RFE       |

|                         | Frequency Modulation | frequency, without harmonics   |                    |

The table 2.1 shows the library of test conditions used for analyzing the performance of PMUs. It can be seen from the table 2.1 that the PMU testing has been broadly classified as steady state tests and dynamic tests. The basic tests mentioned in the IEEE C37.118.1 Standard have been performed, in addition to which the tests have been performed under varying system conditions. It is important to test the PMU with parameter changes under different conditions, especially during the steady state performance analysis, as it is of utmost importance to analyze the behavior of the PMU under such realistic system conditions, for instance voltage and current magnitude changing when harmonics are present at off-nominal frequency conditions. The ranges of parameter or quantity variation (as mentioned in the 2nd column of table 2.1) and the thresholds of performance evaluation criteria (as mentioned in the 4th column of table 2.1) have been nearly kept the same as that mentioned in the standard. The change of system parameters (or quantities) has been scripted in RTDS Runtime as shown in fig. 2.3.

Figure 2.3: Example of RSCAD run case for obtaining test measurements

#### 2.1.2.3 Performance of PMU Testing

Once the library of PMU test conditions is created in the RSCAD-RTDS, the PMU testing is performed in several stages. These include the following –

#### Step-1: Running the individual test cases in the RTDS

The RTDS draft case has the GTNET PMU connected in such a way that it gets the same input measurements as the test PMU. The test PMU gets the low level analog signals from the GTAO card of the RTDS. The GTAO card in turn gets the same input measurements as obtained by the GTNET PMU. With this configuration, individual script files have been written in the RTDS that keep changing the quantities and

parameters automatically as mentioned in table 2.1. These measurements obtained by running the test cases are fed into the GTNET PMU and the test PMU.

Step-2: Collecting the data of the individual test cases in the PDC from the PMUs A PDC (SEL-5073) has been used to collect all the test data of steady state tests and dynamic tests from the PMU under test and the ideal PMU (i.e. the GTNET PMU in the RTDS) as shown in fig. 2.4. Following are the data that are archived in the PDC for the test PMUs and the GTNET PMU –

- -> Time Stamp in the PMU

- -> Voltage Magnitude of Phase A measured by the PMU

- -> Voltage Angle of Phase A measured by the PMU

- -> Voltage Magnitude of Phase B measured by the PMU

- -> Voltage Angle of Phase B measured by the PMU

- -> Voltage Magnitude of Phase C measured by the PMU

- -> Voltage Angle of Phase C measured by the PMU

- -> Current Magnitude of Phase A measured by the PMU

- -> Current Angle of Phase A measured by the PMU

- -> Current Magnitude of Phase B measured by the PMU

- -> Current Angle of Phase B measured by the PMU

- -> Current Magnitude of Phase C measured by the PMU

- -> Current Angle of Phase C measured by the PMU

- -> Frequency measured by the PMU

- -> ROCOF measured by the PMU

Figure 2.4: Example of data archival in software PDC

Step-3: Analysis of the data of the individual test cases based on IEEE-C37.118.1 Standard

Once all the data is archived in the PDC, this archived data is analyzed to find the conformance of the test PMU to the Standard requirements. The performance evaluation parameters for each test (as mentioned in table 2.1) are computed for the test data analysis as per the formulae mentioned in the Standard. Following is a brief description of these performance evaluation parameters -

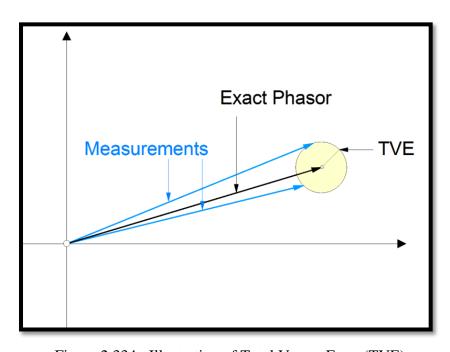

(a) Total Vector Error (TVE) -

$$TVE(n) = \sqrt{\frac{(\hat{X}_r(n) - X_r(n))^2 + (\hat{X}_i(n) - X_i(n))^2}{(X_r(n))^2 + (X_i(n))^2}}$$

Where,  $\widehat{X_r}(n)$  and  $\widehat{X_l}(n)$  are the sequences of estimates given by the test PMU, and Xr(n) and Xi(n) are the sequences of values of the measurements at the instants of time (n) read by the ideal PMU (GTNET PMU).

(b) Frequency Error (FE) -

$$FE = |f_{true} - f_{measured}|$$

Where,  $f_{true}$  is the frequency measured by the ideal PMU (GTNET PMU), and  $f_{measured}$  is the frequency measured by the ideal PMU.

(c) Rate of Change of Frequency or ROCOF Error (RFE) -

RFE = =

$$|(df/dt)_{true} - (df/dt)_{measured}|$$

Where,  $(\frac{df}{dt})_{true}$  is the ROCOF measured by the ideal PMU (GTNET PMU), and  $(\frac{df}{dt})_{true}$  is the ROCOF measured by the test PMU.

### (d) Measurement Response Time -

Measurement response time is the time to transition between two steady-state measurements before and after a step change is applied to the input. It shall be determined as the difference between the time that the measurement leaves a specified accuracy limit and the time it reenters and stays within that limit when a step change is applied to the PMU input. This shall be measured by applying a positive or negative step change in phase or magnitude or frequency to the PMU input signal. The input signal shall be held at a steady-state condition before and after the step change. The only input signal change during this test shall be the parameter that have been stepped.

#### (e) Measurement Delay Time -

Measurement delay time is defined as the time interval between the instant that a step change is applied to the input of a PMU and measurement time that the stepped parameter achieves a value that is halfway between the initial and final steady-state values. Both the step time and measurement time are measured on the UTC time scale. This measurement shall be determined by applying a positive or negative step change in phase or magnitude or frequency to the PMU input signal. The input signal shall be held

at a steady-state condition before and after the step change. The only input signal change during this test shall be the parameter(s) that have been stepped.

#### (f) Peak Overshoot -

This is the maximum value by which the measured value exceeds the final steady state value when a positive step change is applied in phase or magnitude or frequency to the PMU input signal. The input signal shall be held at a steady-state condition before and after the step change. The only input signal change during this test shall be the parameter(s) that have been stepped.

#### 2.1.2.4 Conclusion from Test Results

All the tests mentioned in table 2.1 have been performed on PMUs from different vendors. The nature of PMU behavior are mostly the same qualitatively amongst those tested. In this section, the test conditions and results of 1 test PMU "PMU-A" have been discussed, which is a qualitative representation of the other PMUs that have been tested. Example of system test conditions in RSCAD is shown in fig. 2.5.

#### (A) Discussion on Steady State Tests -

### → Voltage & Current Magnitude Change during balanced system conditions:

Figure 2.5: Test conditions for magnitude change (balanced, nominal)

Figure 2.6: Error analysis for magnitude change (balanced, nominal)

From fig. 2.6, when the system is balanced and is at nominal frequency without harmonics, following observations can be made -

- (i) The voltage TVEs of all the 3 phases are much lesser than the threshold value of 1%.

- (ii) The voltage TVEs of all the 3 phases are not the same.

- (iii) The current TVEs of all the 3 phases are very high (above 1%) when the PMU measures current phasors far below the nominal current value. Gradually, as the current measurement approaches the nominal value, the TVEs decrease and go below the permissible threshold of 1%.

- (iv) The current TVEs of all the 3 phases are not the same.

- (v) On the whole, current TVEs are found to be significantly higher than the voltage TVEs.

- (vi) FE is much below the permissible threshold value.

- (vii) RFE is also much below the allowed threshold value.

→ Voltage & Current Magnitude Change under Off-nominal system frequency conditions:

Figure 2.7: Test conditions for magnitude change (balanced, off-nominal)

Figure 2.8: Error analysis for magnitude change (balanced, off-nominal)

Fig. 2.7 shows system test condition in RTDS. As shown in fig. 2.8, when the system is balanced and is at off-nominal frequency (58 Hz) without harmonics, following observations can be made -

- (i) The voltage TVEs of all the 3 phases are higher than the threshold value of 1%.

- (ii) The voltage TVEs of all the 3 phases are not the same.

- (iii) The current TVEs of all the 3 phases are very much higher than the allowed threshold of 1%.

- (iv) The current TVEs of all the 3 phases are not the same.

- (v) On the whole, current TVEs are found to be significantly higher than the voltage TVEs.

- (vi) FE is much below the permissible threshold value, but is a little higher than the test condition when the system frequency was at nominal value.

- (vii) RFE is higher than the test case when the system frequency was at nominal value. It can be seen that at some point, the RFE also has exceeded the allowed threshold value.

- → Voltage & Current Magnitude Change under when harmonics (3rd, 5th, 7th, and 9th orders) exist in the system:

Figure 2.9: Test conditions for magnitude change (harmonics, nominal)

Figure 2.10: Error analysis for magnitude change (harmonics, nominal)

Fig. 2.9 shows the test conditions and fig. 2.10 shows error analysis. When the system is balanced and is at nominal frequency with harmonics, following observations can be made-

- (i) The voltage TVEs of all the 3 phases are much lesser than the threshold value of 1%.

- (ii) The voltage TVEs of all the 3 phases are not the same.

- (iii) The current TVEs of all the 3 phases are very high (above 1%) when the PMU measures current phasors far below the nominal current value. Gradually, as the current measurement approaches the nominal value, the TVEs decrease and go below the permissible threshold of 1%.

- (iv) The current TVEs of all the 3 phases are not the same.

- (v) On the whole, current TVEs are found to be significantly higher than the voltage TVEs.

- (vi) FE is much below the permissible threshold value. If a comparison is made with the test cases when harmonics are not present, it has been seen that the average FE is much higher when harmonics are present. This is an expected behavior, because of which the IEEE Standard has also increased the permissible threshold value of FE when harmonics are present.

- (vii) RFE is also much below the allowed threshold value. If a comparison is made with the test cases when harmonics are not present, it has been seen that the average RFE is much higher when harmonics are present. This is also an expected behavior, because of which the IEEE Standard has also increased the permissible threshold value of RFE when harmonics are present.

→ Voltage & Current Magnitude Change under Off-nominal system frequency conditions when harmonics are also present:

Figure 2.11: Test conditions for magnitude change (harmonics, off-nominal)

Figure 2.12: Error analysis for magnitude change (harmonics, off-nominal)

Based on test condition of fig. 2.11, and fig. 2.12, when the system is balanced and is at off-nominal frequency with harmonics, following observations can be made -

- (i) The voltage TVEs of all the 3 phases are higher than the threshold value of 1%.

- (ii) The voltage TVEs of all the 3 phases are not the same.

- (iii) The current TVEs of all the 3 phases are very much higher than the allowed threshold of 1%.

- (iv) The current TVEs of all the 3 phases are not the same.

- (v) On the whole, current TVEs are found to be significantly higher than the voltage TVEs.

- (vi) FE is much below the permissible threshold value. If a comparison is made with the test cases when harmonics are not present, it has been seen that the average FE is much higher when harmonics are present. This is an expected behavior, because of which the IEEE Standard has also increased the permissible threshold value of FE when harmonics are present.

- (vii) RFE is also much below the allowed threshold value. If a comparison is made with the test cases when harmonics are not present, it has been seen that the average RFE is much higher when harmonics are present. This is also an expected behavior, because of which the IEEE Standard has also increased the permissible threshold value of RFE when harmonics are present.

- (viii) Amongst all the test conditions discussed above when the voltage and current magnitudes are changed, the performance of the PMU deteriorates the most when the system is at off-nominal frequency and also has harmonics.

- → Voltage & Current Angle Change under balanced system conditions:

Figure 2.13: Test conditions for angle change (balanced, nominal)

Figure 2.14: Error analysis for angle change (balanced, nominal)

From fig. 2.13 and fig. 2.14, when the system is balanced and is at nominal frequency without harmonics, following observations can be made –

- (i) The voltage TVEs of all the 3 phases are much lesser than the threshold value of 1%.

- (ii) The voltage TVEs of all the 3 phases are not the same.

- (iii) The current TVEs of all the 3 phases are lesser than the permissible threshold of 1%.

- (iv) The current TVEs of all the 3 phases are not the same.

- (v) On the whole, current TVEs are found to be higher than the voltage TVEs.

- (vi) FE is much below the permissible threshold value.

- (vii) RFE is also much below the allowed threshold value.

- → Voltage & Current Angle Change under when harmonics (3rd, 5th, 7th, and 9th orders) exist in the system:

From fig. 2.15 and 2.16 when the system is balanced and is at nominal frequency with harmonics, following observations can be made –

- (i) The voltage TVEs of all the 3 phases are much lesser than the threshold value of 1%.

- (ii) The voltage TVEs of all the 3 phases are not the same.

- (iii) The current TVEs of all the 3 phases are very high (above 1%) irrespective of the current magnitude.

- (iv) The current TVEs of all the 3 phases are not the same.

- (v) On the whole, current TVEs are found to be significantly higher than the voltage TVEs.

- (vi) FE is much below the permissible threshold value. If a comparison is made with the test cases when harmonics are not present, it has been seen that the average FE is much higher when harmonics are present. This is an expected behavior, because of which the IEEE Standard has also increased the permissible threshold value of FE when harmonics are present.

- (vii) RFE is also below the allowed threshold value. If a comparison is made with the test cases when harmonics are not present, it has been seen that the average RFE is much higher when harmonics are present. This is also an expected behavior, because of which the IEEE Standard has also increased the permissible threshold value of RFE when harmonics are present.

Figure 2.15: Test conditions for angle change (harmonics, nominal)

Figure 2.16: Error analysis for angle change (harmonics, nominal)

→ Frequency Change under balanced system conditions:

Figure 2.17: Test conditions for frequency change (balanced)

Figure 2.18: Error analysis for frequency change (balanced)

Based on test conditions in fig. 2.17 and error analysis from fig. 2.18, when the system is balanced without harmonics, following observations can be made -

- (i) The voltage TVEs of all the 3 phases are much lesser than the threshold value of 1% when the system is at nominal frequency (60 Hz). However, as the system frequency moves away from the nominal value both, above and below, the TVEs start increasing rapidly. It can be seen that at 58 Hz and 62 Hz, the voltage TVEs exceed the threshold value of 1%.

- (ii) The voltage TVEs of all the 3 phases are not the same.

- (iii) The current TVEs of all the 3 phases are lesser than the threshold value of 1% when the system is at nominal frequency (60 Hz). However, as the system frequency moves away from the nominal value both, above and below, the TVEs start increasing rapidly. It can be seen that at 58 Hz and 62 Hz, the current TVEs exceed the threshold value of 1%.

- (iv) The current TVEs of all the 3 phases are not the same.

- (v) On the whole, current TVEs are found to be higher than the voltage TVEs.

- (vi) FE is much below the permissible threshold value.

- (vii) RFE is also below the allowed threshold value.

Figure 2.19: Test conditions for frequency change (balanced, harmonics)

Figure 2.20: Error analysis for frequency change (balanced, harmonics)

From fig. 2.19 and fig. 2.20, when the system is balanced with harmonics, following observations can be made -

- (i) The voltage TVEs of all the 3 phases are much lesser than the threshold value of 1% when the system is at nominal frequency (60 Hz). However, as the system frequency moves away from the nominal value both, above and below, the TVEs start increasing rapidly. It can be seen that at 58 Hz and 62 Hz, the voltage TVEs exceed the threshold value of 1%.

- (ii) The voltage TVEs of all the 3 phases are not the same.

- (iii) The current TVEs of all the 3 phases are mostly higher than the threshold value of 1% and are quite random independent of the frequency values unlike voltage TVEs.

- (iv) The current TVEs of all the 3 phases are not the same.

- (v) On the whole, current TVEs are found to be higher than the voltage TVEs.

- (vi) FE is much below the permissible threshold value.

- (vii) RFE is also below the allowed threshold value.

- (B) Discussion on Dynamic Tests -

- → Voltage Magnitude Step Change:

Figure 2.21: Response during step change in voltage magnitude

Following are the analytical results of the PMU performance during the step change in voltage magnitude (fig. 2.21) -

Table 2.2: Test results for response to magnitude step change

| <b>Evaluation Parameters</b> | Results of the Test PMU | Allowable Values as per IEEE-C37.118.1 |

|------------------------------|-------------------------|----------------------------------------|

| Response Time (in seconds)   | 0.093                   | 0.182                                  |

| Delay Time (in seconds)      | 0.065                   | 0.008                                  |

| % Peak Overshoot             | 0.279                   | 10                                     |

From the results table 2.2, it can be seen that the PMU under test -

- (i) Meets the requirement of response time.

- (ii) Does not meet the requirement of delay time

- (iii) Meets the requirement of % peak overshoot

# → Voltage Angle Step Change:

Figure 2.22: Response during step change in voltage angle

Table 2.3: Test results for response to angle step change

| <b>Evaluation Parameters</b> | Results of the Test PMU | Allowable Values as per IEEE-C37.118.1 |

|------------------------------|-------------------------|----------------------------------------|

| Response Time (in seconds)   | 0.113                   | 0.182                                  |

| Delay Time (in seconds)      | 0.045                   | 0.008                                  |

| % Peak Overshoot             | 2.561                   | 10                                     |

From the results as shown in fig. 2.22 and table 2.3, it can be seen that the PMU under test-

- (i) Meets the requirement of response time.

- (ii) Does not meet the requirement of delay time

- (iii) Meets the requirement of % peak overshoot

# → Frequency Step Change:

Figure 2.23: Response during step change in frequency

Table 2.4: Test results for response to frequency step change

| <b>Evaluation Parameters</b> | <b>Results of the Test PMU</b> | Allowable Values as per |

|------------------------------|--------------------------------|-------------------------|

|                              |                                | IEEE-C37.118.1          |

| Response Time (in seconds)   | 0.267                          | 0.305                   |

| ROCOF Response Time          | 0.4                            | 0.314                   |

| (in seconds)                 |                                |                         |

| Delay Time (in seconds)      | 0.08                           | 0.008                   |

| % Peak Overshoot             | 0.042                          | 10                      |

From the results shown in fig. 2.23 and table 2.4, it can be seen that the PMU under test -

- (i) Meets the requirement of frequency response time

- (ii) Does not meet the requirement of ROCOF response time

- (iii) Does not meet the requirement of delay time

- (iv) Meets the requirement of % peak overshoot

# → Frequency Ramp Change:

Figure 2.24: Response during ramp change in frequency

Table 2.5: Test results for response to frequency ramp change

| Evaluation Parameters | Results of the Test PMU | Allowable Values as per IEEE-C37.118.1 |

|-----------------------|-------------------------|----------------------------------------|

| Maximum FE (in Hz)    | 0.083                   | 0.005                                  |

| Maximum RFE (in Hz/s) | 0.457                   | 0.1                                    |

From the results as shown in fig. 2.24 and table 2.5, it can be seen that the PMU under test-

- (i) Does not meet the requirement of FE

- (ii) Does not meet the requirement of RFE

# → Amplitude, Phase & Frequency Modulation Changes:

From fig. 2.25 and 2.26, when the amplitude, phase and frequency modulation is done in the system, following observations can be made -

- (i) The voltage TVEs of all the 3 phases are much higher than the threshold value of 1%.

- (ii) The voltage TVEs of all the 3 phases are not the same.

- (iii) The current TVEs of all the 3 phases are much higher than the threshold value of 1%

- (iv) The current TVEs of all the 3 phases are not the same.

Figure 2.25: Dynamic test conditions for change in modulated signal

Figure 2.26: Error analysis of the test PMU under given system condition

- (v) On the whole, current TVEs are found to be higher than the voltage TVEs.

- (vi) FE is much higher than the permissible threshold value.

- (vii) RFE is initially below the allowed threshold limit. But as the frequency modulation increases, the RFE goes on increasing rapidly, and exceeds the allowed threshold value.

From the analysis of the steady state and dynamic tests, it can be seen that the PMU under test behaves differently under different system conditions. The tests performed on the PMU under test provides a comprehensive coverage of the performance of the PMU. It has been seen that the PMU under test satisfies most of the test criteria as mentioned in the standard, but fails some of them.

## 2.2.3 PDC Testing

#### 2.1.3.1 Introduction

A Phasor Data Concentrator (PDC) works as a node in a communication network where synchrophasor data from a number of PMUs or PDCs is processed and fed out as a single stream to the higher level PDCs and/or applications. Synchrophasor data may include time stamped 3-phase voltage magnitudes, voltage angles, current magnitudes, current angles, frequency, rate of change of frequency (ROCOF), real and reactive power, digital signals like circuit breaker switch status, etc. The PDC processes synchrophasor data by timestamp to create a system-wide measurement set.

PDCs can have several modes of operation. For instance, the local PDCs aggregate and time-align synchrophasor data from multiple PMUs in a substation and feed the data to applications. Mid-level and higher-level PDCs collect synchrophasor data from multiple PDCs, conduct data quality checks, time align the data and feed the data to applications. The PDCs may be recognized as a function rather than as a stand-alone device or hardware/software package, and can be integrated into other systems and devices. A structured hierarchy of distributed PDCs may be formed to serve a hierarchy of systems: substation, utility, control area, reliability coordinator, and interconnection level. Distributed PDCs may also interact with each other on a peer-to-peer basis among utilities, control areas, and reliability coordinators.

A PDC is expected to perform some of the important functions in the synchrophasor infrastructure as stated below -

#### (a) Data Aggregation -

This is the basic function of a PDC. It refers to the streaming and accumulation of the synchrophasor data from the PMU(s) in the PDC. The data aggregation functionality of a PDC is required for real time system monitoring as well as post-event analysis. Data aggregation function could be performed with or without time alignment. It should preserve data quality, time quality, and time synchronization indications from each signal, and include the data quality information assigned by the individual sending devices to the output data frames.

Data coming into a PDC has been time stamped by the PMU with a time referenced to UTC, absolute time. Data aggregation with time alignment refers to waiting for data with a given timestamp from all sources, placing that data in a packet, and forwarding it. The PDC aligns the data received from PMU/PDC according to their timestamps, not their arriving order or arriving time. Time alignment to absolute time refers to waiting no more than a specified absolute wait time after a timestamp time for data with that timestamp. This requires that the PDC is synchronized to UTC. Time alignment to relative time refers to waiting no more than a specified relative wait time after an event. An event may be the arrival of the first data with a specific timestamp.

For some applications, it is desirable to receive a set of synchrophasor measurements with minimum latency. However, to reduce data loss due to late data arrival, longer wait times are needed, which in turn increase latency. To address these conflicting requirements i.e. no loss of data due to late arrival and minimum latency, a PDC could aggregate all the data required for the output destination without time alignment and transmit it periodically.

## (b) Data Forwarding -

To minimize PDC latency, a PDC needs to support data forwarding. Data forwarding is performed either from one input to one output, or from one input to multiple outputs. No data aggregation is performed in this case. Data forwarding can be performed without data modification or with data modifications that may include data format and coordinate conversion, phase and magnitude adjustments (for calibration purposes), decimation, interpolation, etc.

#### (c) Data Validation -

A PDC is supposed to perform basic data validation and check the data arriving at the PDC. This includes checking the time quality of all PMUs as well as the data status flags. For this purpose, data integrity checks such as cyclic redundancy check [CRC] can be performed on all received data. Any errors detected and suspected corrupt data should be flagged in output data stream(s).

# (d) Data Communication -

This function allows a PDC to connect with other devices via serial and Ethernet based communication networks so that the PDC can receive synchrophasor data. The synchrophasor system communications include both data (streaming data and configuration information) and command communications. Data transfer is typically client-server based using either auto-initiation or a data request command. In the auto-initiation mode, data transmission is implemented without waiting for any request from any destination devices/applications for each individual data point in the series. In the data request command mode of operation a client (the PDC) sends a data request command to the server (a PMU or another PDC). The server then responds with the requested data. The data communications in a synchrophasor system could be one-to-one (i.e., from one source to one destination) and/or one-to-many (i.e., from one source to multiple destinations). Either mode may be implemented on Ethernet based networks, but serial networks are generally one-to-one unless the serial connection is specially modified

to allow a one-to-many connection. The command communications of a synchrophasor system includes various synchrophasor command frames. For example for IEEE Std C37.118.2-2011, the synchrophasor command frames provide commands to the PMU to initiate streaming, to stop streaming, to retrieve the header frame, to retrieve the configuration frame, and to execute user-defined controls. The command communications of a synchrophasor system may be one-to-one using serial or Ethernet networks. When using Ethernet networks, command communications typically uses TCP over IP, but can also use UDP over IP. Command communications are independent of the protocols used for the data transmission.

# (e) Data Transfer Protocols Support and Conversion -

Synchrophasor data from PMUs may be available in different synchrophasor data transfer protocols such as IEEE Standard C37.118, IEEE Standard 1344-1995, IEC 61850-90-5, etc. A PDC should be able to support at least one of these protocols for seamless streaming of data from the PMU(s) it is connected to. If a PDC supports multiple synchrophasor data transfer protocols, it should convert synchrophasor data from one synchrophasor data transfer protocol to another to the extent possible.

# (f) Data Latency Computation -

In a packet-switched network, data latency is the time delay between a sender transmitting a packet and a user receiving it. Because communication traffic volume and errors in transmission can affect intermediate delays, latency is sometimes not very predictable. Applied to the PMU/PDC system, there are multiple sources of synchrophasor data latency could be due to the following reasons -

- (i) Physical distance between the two ends of the system,

- (ii) Processing of the packet in intermediate network devices,

- (iii) PMU calculation and processing time,

- (iv) PMU-PDC data transmission time,

- (v) PDC processing time.

Data latency will be different at different points in a hierarchical data network. It will increase cumulatively at successive data destinations such as the substation PDC, the TO control center PDC, the ISO control center PDC.

#### (g) Reporting Rate Conversion -

The reporting rate conversion refers to the change of the reporting rate of a data stream to be different from the input data stream (e.g., 30 frames per second (fps) to 15 fps, or 30 fps to 60 fps). Reporting rate conversion functions are very useful for -

- (i) Merging synchrophasor data arriving at different reporting rates from different sources,

- (ii) Converting available data to a rate that is most suitable for a specific application using synchrophasor data.

A PDC should ideally include both down-conversion and up-conversion functions. If this function is not provided, it should be clearly stated in the PDC's specification by the manufacturer. Along with this, any limitations in the conversion functions should also be specified. The PDC should support input rate conversion from all rates specified in IEEE

Standard C37.118.1-2011 to output streams having any rate specified in IEEE Std C37.118.1-2011. Reporting rate conversion should be user-configurable to accommodate the compatibility needs of all the devices and applications in the synchrophasor system, as well as all the applications that might be using the data from the PDC.

## (h) Data Adjustments -

The PDC function requires the incoming data to be either copied into the output data stream, or converted to a different format (e.g., rectangular/polar, floating/fixed point). The data are expected to be essentially unchanged. However, at times, a PDC may be required to perform magnitude or phase adjustments on the incoming signal. There could be two types of such adjustments:

- (i) Calibration type adjustments,

- (ii) Bulk type adjustments.

Each of these adjustments is expected to be set manually, based on calibration factors, phase rotation sequence, transformer ratios, phase angles, etc. Calibration type adjustments are those that require small changes to the magnitude/phase of a signal, typically within 5% of the magnitude, or within 5 degrees of the phase. The purpose of calibration adjustments is to compensate for errors in the measurement chain. These may be useful for a PDC, especially for a substation PDC, but generally, this function is performed in a PMU. Bulk type phase and magnitude adjustments are those that require large changes to the phase/magnitude of a synchrophasor signal. These are useful, for example, when a signal needs to be referenced across a transformer when the phase identification of the destination system is different (ABC versus ACB) from the source system, or when the quantities are being referenced across a wye-delta (or star-delta) transformer.

## 2.1.3.2 Library of Test Conditions

Test No.

PDC Functionality Test

1. Time Alignment of Data

2. Data Validation

3. Data Loss

4. Data Latency

5. Reporting Rate Conversion

6. Format & Coordinate Conversion

7. Phase & Magnitude Adjustment

Table 2.6: Library of PDC tests

IEEE Standard for PDC testing C37.244-2013 specifies the tests that need to be performed on PDCs. From the pool of tests, some of the important tests have been performed at SGDRIL, WSU. Table 2.6 provides the library of test conditions. The descriptions of the functionality tests have been provided in Section 2.1.3.1.

# 2.1.3.3 Performance of PDC Testing

Two different test beds have been created for testing PDCs. Fig. 2.27 provides the functional schematic diagram of the test bed used for performing PDC tests where data loss due to long distance communication issues has not been tested. This simulates an environment in which the PMU and the PDC are located in the same substation. Fig. 2.28 provides the functional schematic diagram of the test bed used for performing PDC tests where data loss due to long distance communication issues has also been tested. This simulates an environment in which the PMU and the PDC are located in the different substations or the PMU is sending data from a substation to a PDC located in the control center.

Figure 2.27: Test bed for testing PDCs without communication modeling

Figure 2.28: Test bed for testing PDCs with communication model

In fig. 2.28, NS3 i.e. Network Simulator 3 has been used to model long distance communication delays and latencies in a system network. NS3 is a discrete-event simulator targeted primarily for research and educational use and is an open-source project. It is the successor to the highly popular NS2, but NS3 has been written from scratch and not derived from NS2. It uses C++ for scripting with python bindings. NS3 supports emulation mode of operation and has the ability to simulate communication issues in real time.

#### 2.1.3.4 Conclusion from Test Results

(A) Discussion on Test-1: Time Alignment of Data

Table 2.7: Test results for time alignment (rate = 30 frames / second)

| Time Duration of Data Collection in | Number of Data<br>Frames Streamed | Number of Time<br>Alignment Errors | Number of Time<br>Alignment Errors |

|-------------------------------------|-----------------------------------|------------------------------------|------------------------------------|

| PDCs                                |                                   | in PDC-A                           | in PDC-B                           |

| 30 minutes                          | 54000                             | 0                                  | 0                                  |

| 1 hour                              | 108000                            | 0                                  | 0                                  |

| 6 hours                             | 648000                            | 0                                  | 0                                  |

| 12 hours                            | 1296000                           | 0                                  | 0                                  |

| 24 hours                            | 2592000                           | 0                                  | 0                                  |

Table 2.8: Test results for time alignment (rate = 60 frames / second)

| Time Duration of<br>Data Collection in<br>PDCs | Number of Data<br>Frames Streamed | Number of Time<br>Alignment Errors<br>in PDC-A | Number of Time<br>Alignment Errors<br>in PDC-B |

|------------------------------------------------|-----------------------------------|------------------------------------------------|------------------------------------------------|

| 30 minutes                                     | 108000                            | 0                                              | 0                                              |

| 1 hour                                         | 216000                            | 0                                              | 0                                              |

| 6 hours                                        | 1296000                           | 0                                              | 0                                              |

| 12 hours                                       | 2592000                           | 0                                              | 0                                              |

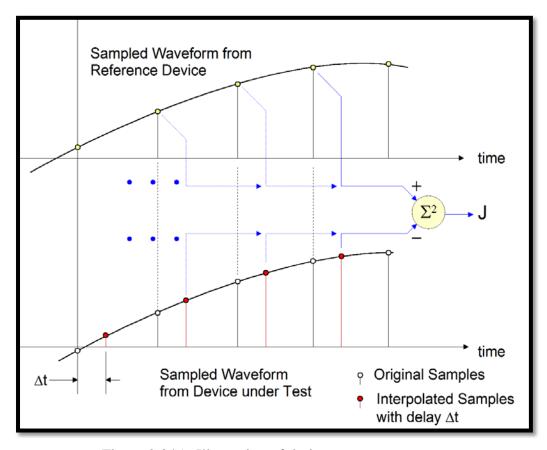

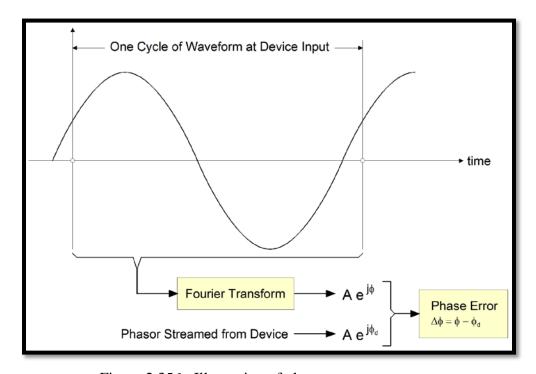

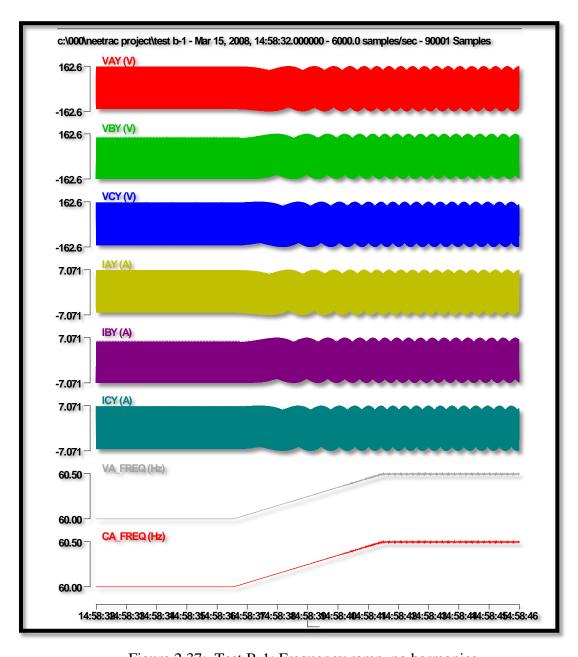

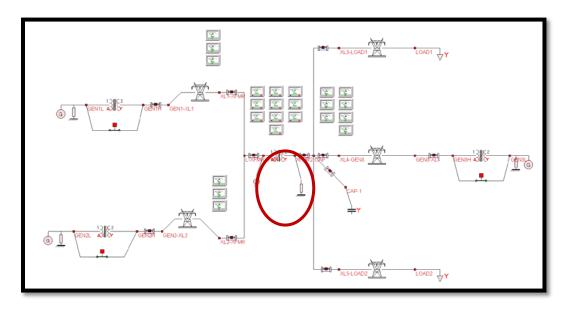

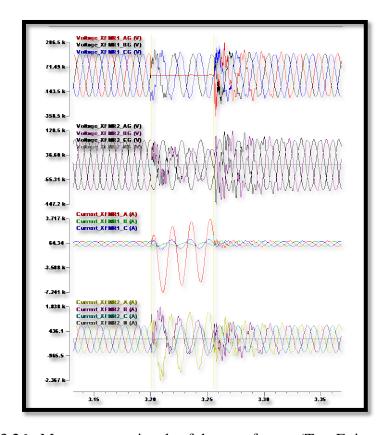

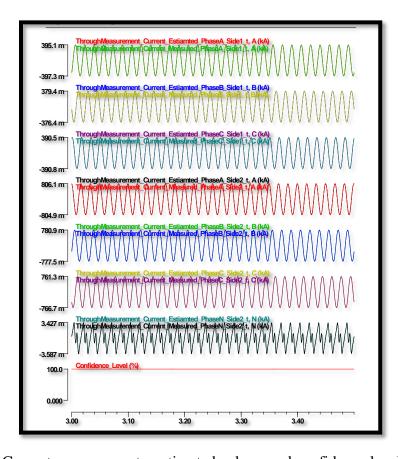

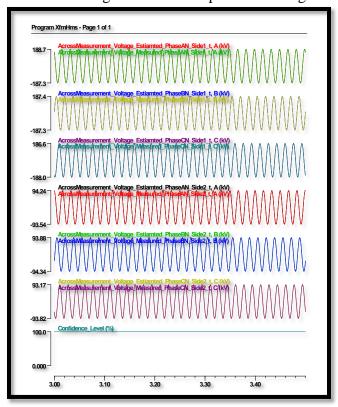

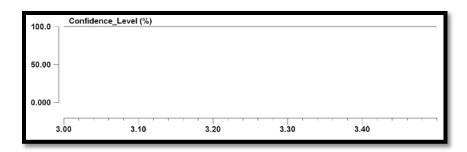

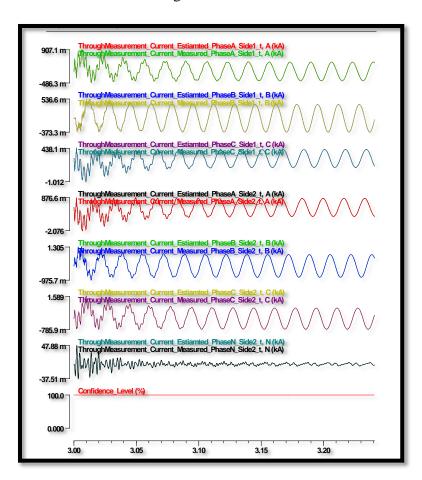

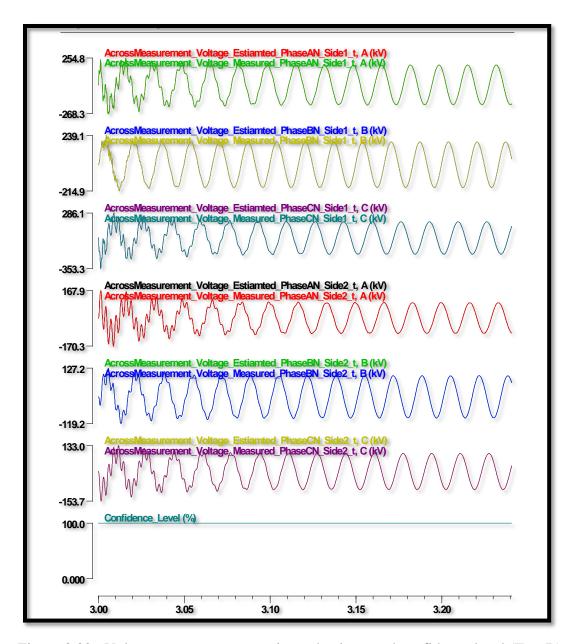

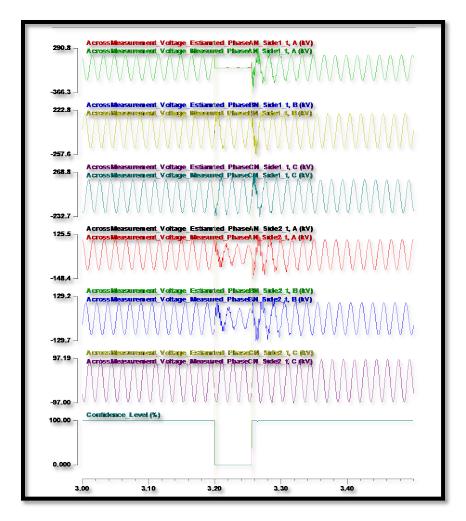

| 24 hours                                       | 5184000                           | 0                                              | 0                                              |